PAPER Special Section on Analog Circuits and Their Application Technologies

# **Sub-60-mV Charge Pump and its Driver Circuit for Extremely Low-Voltage Thermoelectric Energy Harvesting**

Hikaru SEBE<sup>†a)</sup>, Nonmember, Daisuke KANEMOTO<sup>†</sup>, and Tetsuya HIROSE<sup>†b)</sup>, Members

SUMMARY Extremely low-voltage charge pump (ELV-CP) and its dedicated multi-stage driver (MS-DRV) for sub-60-mV thermoelectric energy harvesting are proposed. The proposed MS-DRV utilizes the output voltages of each ELV-CP to efficiently boost the control clock signals. The boosted clock signals are used as switching signals for each ELV-CP and MS-DRV to turn switch transistors on and off. Moreover, reset transistors are added to the MS-DRV to ensure an adequate non-overlapping period between switching signals. Measurement results demonstrated that the proposed MS-DRV can generate boosted clock signals of 350 mV from input voltage of 60 mV. The ELV-CP can boost the input voltage of 100 mV with 10.7% peak efficiency. The proposed ELV-CP and MS-DRV can boost the low input voltage of 56 mV.

key words: energy harvesting, power management circuit, voltage boost converter, cold-start circuit, start-up circuit, charge pump, driver circuit

## 1. Introduction

A large number of IoT (Internet of Things) edge node devices connected to the network will be installed everywhere. They will be an up-and-coming intelligent communication platform for collecting and delivering information throughout the world. However, maintenance and replacement of the batteries of these battery-powered devices are crucial issues. To address those issues, energy harvesting has attracted extensive attention as an autonomous energy sources for IoT edge node devices [1]–[7].

Thermoelectric generators (TEGs) can generate electrical energy from a slight difference in temperature. However, output voltage of a TEG,  $V_{\rm TEG}$ , is too low to operate LSI systems and sensors when temperature difference is a few degrees (e.g.,  $V_{\rm TEG}$ s are less than several tens of millivolts). An ultra-low-power and highly efficient power-management circuit (PMC) is therefore required [3]–[9].

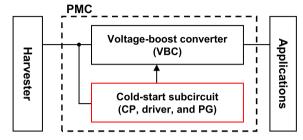

Figure 1 shows a block diagram of a PMC using a TEG energy harvester. The PMC consists of a voltage-boost converter (VBC) and a cold-start subcircuit. The cold-start subcircuit must operate at low voltage  $V_{\rm IN}$  and generate control signals for the VBC. For that purpose, a multi-stage charge pump (CP) and its driver (DRV) circuit are extensively used to convert low  $V_{\rm IN}$  to a higher output voltage [10]–[21]. However, the control signals generated by the driver significantly

Manuscript received November 2, 2023.

Manuscript revised February 26, 2024.

Manuscript publicized April 9, 2024.

<sup>†</sup>Graduate School of Engineering, Osaka University, Suita-shi, 565–0871 Japan.

a) E-mail: sebe@ssc.eei.eng.osaka-u.ac.jpb) E-mail: hirose@eei.eng.osaka-u.ac.jpDOI: 10.1587/transele.2023CTP0005

**Fig. 1** Power management circuit for low-voltage energy harvesting (©2022 IEEE [24]).

degrade as  $V_{\rm IN}$  decreases; therefore, the conventional multistage CP cannot generate a sufficient output voltage when  $V_{\rm IN}$  is low. Appropriate control signals cannot be obtained even though multi-stage drivers are connected in cascade.

To solve the above-described problem, we propose an extremely low-voltage CP (ELV-CP) and its dedicated multistage driver (MS-DRV) for sub-60-mV energy harvesting. The proposed MS-DRV utilizes the output voltages of each ELV-CP to efficiently boost control signals. The boosted clock signals are used as switching signals for each ELV-CP and MS-DRV to turn switch transistors on and off at low  $V_{\rm IN}$  [22], [23]. Moreover, reset transistors are added to the MS-DRV to ensure an adequate non-overlapping (NOL) period between switching signals. In contrast to our previous work [24], we add some simulation results and discuss its circuit operation in more detail. In addition, we fabricate a proof-of-concept chip using a 180-nm CMOS process and demonstrate the effectiveness of our proposed circuits. The proposed ELV-CP and MS-DRV can operate at extremely low  $V_{\rm IN}$  of 56 mV.

This paper is organized as follows: Section 2 briefly describes conventional CP and DRV and explains the issues concerning them; Section 3 presents the proposed ELV-CP and MS-DRV; Section 4 shows the results of simulations; Section 5 discusses the results of measurements; and Sect. 6 concludes the paper.

## 2. Conventional CP and DRV

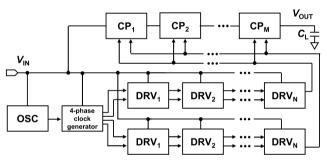

Figure 2 shows a block diagram of conventional CP and its DRV [25], [26]. A high voltage-conversion ratio (VCR) can be realized by connecting *n*-stage CPs in cascade. For the multi-stage CP, a DRV is required to turn the switch transistors in the CPs on and off. As shown in Fig. 2, the boosted clock signals can also be generated by connecting

*n*-stage DRVs in cascade.

It should be noted that it is difficult to obtain higher boosted clock signals because the voltage-boost ratio of the n-stage DRVs is limited by n+1. In addition, conventional CPs use a 4-phase clock generator, which consists of a NOL clock generator and some logic gates, to control the switch transistors in the DRVs [25], [26]. However, when the clock signals are applied to the DRVs, the timing of the signals is delayed, so a multi-stage DRV cannot generate NOL boosted clock signals. The number of the drivers is therefore limited to less than 3 or 4; thus, higher clock signals cannot be obtained stably.

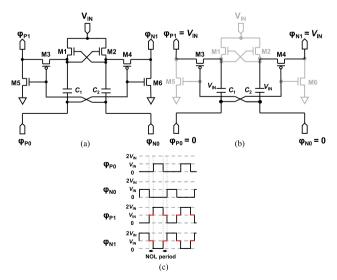

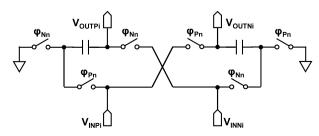

Note that a conventional DRV cannot operate correctly with NOL clock signals. Figure 3 shows schematics of a conventional driver [26] and its operation when NOL clock signals are both low, namely,  $\varphi_{P0} = \varphi_{N0} = 0$ , and its time chart. Under the condition, both of the top potentials of  $C_1$  and  $C_2$  are  $V_{IN}$ , and PMOS switch transistors M3 and M4 are turned on, as shown in Fig. 3 (b) (in which switch transistors colored in gray are turned off). Therefore, both output voltages become  $V_{IN}$ . In other words, the NOL period of the output voltages cannot be obtained when  $\varphi_{P0} = \varphi_{N0} = 0$ , so operation of the multi-stage DRV circuit fails. Consequently, a 4-phase clock generator is conventionally used to control

Fig. 2 Block diagram of conventional CP and its driver [25], [26].

**Fig. 3** Schematics of (a) conventional driver, (b) its operation when  $\varphi_{P0} = \varphi_{N0} = 0$  (switch transistors colored in gray are turned off), and (c) time chart.

switching timing [25], [26].

To solve the above-described problems, a low-voltage CP and DRV are proposed and described in detail in the next section.

## 3. Proposed ELV-CP and MS-DRV

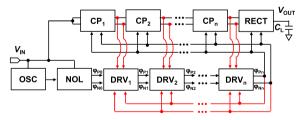

Figure 4 shows a block diagram of the proposed ELV-CP and its MS-DRV. The proposed circuits are based on the conventional one, except the DRV is modified to generate higher-boosted clock signals with adequate NOL period [26]. Note that a dual-input and dual-output CP as reported in [27] is used, and the output voltages of the CP change between  $V_{\rm IN}$  and  $2V_{\rm IN}$  alternately, as shown in Fig. 5. A conventional rectifier (RECT) is used to obtain the output voltage  $V_{\rm OUT}$  [27].

Differing from the conventional design, the proposed MS-DRV accepts output voltages of each CP to boost the control signals, as shown in Fig. 4. Voltage-boost ratio of the n-stage MS-DRV can therefore be increased to  $2^n$ , which is much higher than the conventional design of n+1. In addition, each MS-DRV accepts the boosted clock signals  $\varphi_{Pn}$  and  $\varphi_{Nn}$  to improve the performance of the switch transistors in the MS-DRV.

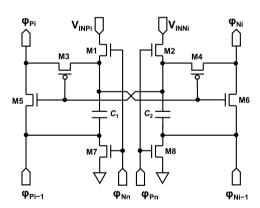

Figure 6 shows a schematic of the first stage of the proposed MS-DRV. Input NOL signals  $\varphi_{P0}$  and  $\varphi_{N0}$  are applied to the MS-DRV, and boosted NOL signals  $\varphi_{P1}$  and  $\varphi_{N1}$  are then generated. The output voltages of  $CP_1$  are applied to  $V_{INP1}$  and  $V_{INN1}$ . They determine the voltage-boost ratio of  $\varphi_{P1}$  and  $\varphi_{N1}$ . The boost ratio is determined by one of the two CP's output voltages. In this design, we use a lower output voltage of the CP's output voltages because the leakage loss increases when the higher output voltage is used. Boosted control signals  $\varphi_{Pn}$  and  $\varphi_{Nn}$  are applied to the MS-DRV in opposite-phase relation, as shown in Fig. 6.

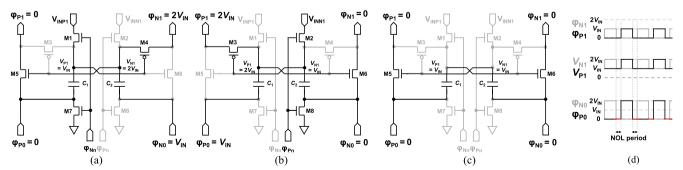

Figure 7 illustrates operation of the proposed MS-DRV and its time chart. The operation principles are given as follows:

Fig. 4 Block diagram of proposed ELV-CP and its MS-DRV.

Fig. 5 Schematic of CP [27]

- 1. When input signals  $(\varphi_{P0}, \varphi_{N0})$  are  $(0, V_{IN})$ , top potentials  $C_1$  and  $C_2$  are  $V_{IN}$  and  $2V_{IN}$ , respectively. The output signals  $(\varphi_{P1}, \varphi_{N1})$  become  $(0, 2V_{IN})$  because switch transistors M4 and M5 are turned on. The boosted signal  $(\varphi_{N1} = 2 \times V_{IN})$  can be obtained (see Fig. 7 (a)).

- 2. When input signals  $(\varphi_{P0}, \varphi_{N0})$  are  $(V_{IN}, 0)$ , top potentials  $C_1$  and  $C_2$  are  $2V_{IN}$  and  $V_{IN}$ , respectively. The output signals  $(\varphi_{P1}, \varphi_{N1})$  become  $(2V_{IN}, 0)$  because switch transistors M3 and M6 are turned on. The boosted signal  $(\varphi_{P1} = 2 \times V_{IN})$  can be obtained (see Fig. 7 (b)).

- 3. When input signals  $(\varphi_{P0}, \varphi_{N0})$  are (0,0), top potentials  $C_1$  and  $C_2$  are both  $V_{IN}$ . The output signals  $(\varphi_{P1}, \varphi_{N1})$  become (0,0) because reset transistors M5 and M6 are turned on. In this way, the NOL period can be obtained (see Fig. 7 (c)).

Although operation of the proposed MS-DRV was explained by using the first stage of the MS-DRV as an example, the same discussion can be applied to the following drivers.

Note that it is important to point out the cold-start operation of the proposed MS-DRV. When the ELV-CP has not been charged yet during the cold-start period, the output voltage of the MS-DRV cannot be boosted. The output-voltage swing at the last stage of the MS-DRV is therefore given as  $V_{\rm IN}$ . However, the output voltage of the ELV-CP is increased by the clock signals, so the output voltage of the MS-DRV also increases. With the mutual relationship between the CPs and DRVs, the output voltage of the ELV-CP increases

**Fig. 6** Schematic of proposed DRV.

gradually even though the ELV-CP is not precharged.

### 4. Simulation Results

The performance of the proposed ELV-CP and MS-DRV was evaluated by SPICE with a set of 180-nm CMOS process parameters. A three-stage CP and its driver were designed and evaluated. The ideal voltage-conversion ratio (VCR) of the CP was 8 (=  $2^3$ ). All the capacitors were MIM (Metal-Insulator-Metal) capacitors. The charge-transfer capacitors of the first, second, and third CP were set to 55.0, 27.5, and 13.8 pF, respectively. All the capacitors in the DRV and output capacitors were set to 28.8 and 36 pF, respectively. To generate NOL clock signals from  $V_{\rm IN}$ , a ring oscillator (ROSC) and an NOL clock generator capable of extremely low-voltage operation were used and designed [17], [28]–[31]. In the simulations,  $V_{\rm IN}$  was set to 60 mV for waveforms and 100 mV for other simulations. The output resistance was set to 5  $\Omega$ .

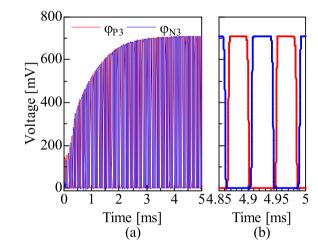

Figures 8 (a) and 8 (b) show the simulated output waveforms of the proposed MS-DRV,  $\varphi_{P3}$  and  $\varphi_{N3}$ , and their partial enlarged view, respectively. The voltage swings were 712.6 mV. It is clear that the boosted clock signals were successfully obtained. As shown in Fig. 8 (b), they also have enough NOL time. However, the voltage swings were

**Fig. 8** (a) Simulated waveforms of proposed DRV and (b) its partial enlarged view.  $V_{\rm IN}$  was set to 100 mV (©2022 IEEE [24]).

**Fig. 7** Operation of the driver: (a)  $(\varphi_{P0}, \varphi_{N0}) = (0, V_{IN})$ , (b)  $(\varphi_{P0}, \varphi_{N0}) = (V_{IN}, 0)$ , (c)  $(\varphi_{P0}, \varphi_{N0}) = (0, 0)$ , and (d) its time chart. Switch transistors colored in gray represent off transistors.

Fig. 9 Simulated transient output voltage of CP (©2022 IEEE [24]).

Fig. 10 Simulated output voltage as a function of load current.

slightly lower than the ideal voltage swings of 800 mV. This was because of the leakage currents of the switch transistors in the ELV-CP and MS-DRV.

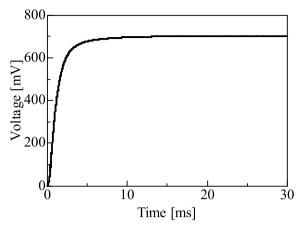

Figure 9 shows the simulated transient waveform of the ELV-CP's output voltage under no load. The output voltage increased gradually and settled to 702.5 mV in a steady state.

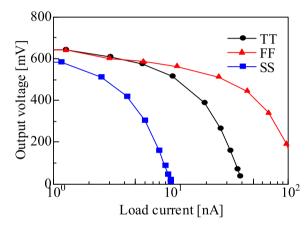

Figure 10 shows the simulated load-current dependence of output voltage of the ELV-CP at different process corners. In the simulation, we considered typical-typical, fast-fast, and slow-slow (TT, FF, and SS) corners. Slow-fast and fastslow (SF and FS) corners were not taken in account because it is well known that low-voltage CMOS circuits are hard to operate at the corners [20]. Output voltage decreased as the load current increased. The load-current ranges that can supply output voltage of more than 400 mV at the SS, TT, and FF corners were limited to less than 4, 10, and 44 nA, respectively. This was because the charge transport capability of the ELV-CP depended on the frequency of the ROSC and the frequency changed according to the process corners. As for this cold-start application, the load range is considered acceptable because it is assumed that the generated voltage is used as the supply voltage for the pulse generator [16], [17].

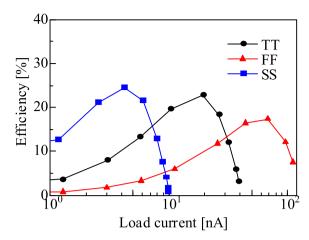

Figure 11 shows the power conversion efficiency (PCE) as a function of  $I_{\rm load}$  at different process corners. The power

Fig. 11 Simulated power-conversion efficiency as a function of load current.

Fig. 12 Simulated VCR as a function of input voltage.

dissipation of the ROSC and NOL clock generators was also taken into account. Maximum PCEs at TT, FF, and SS corners were 22.8, 17.4, and 24.5% at 100-mV input voltage and 19.4-, 68.1- and 4.2-nA load current, respectively. As the load current increased, the PCEs decreased due to the on-resistance of the transistors. PCE can also be improved by using larger capacitors in the CP.

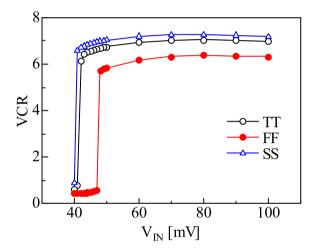

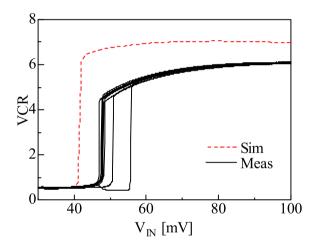

Figure 12 shows the VCR as a function of input voltage at different process corners. VCRs at TT, FF and SS corners were higher than 5 when input voltage was higher than 42, 48 and 41 mV, respectively. However, VCR dropped steeply below these voltages, because the open-loop-voltage gain through ELV-CP and MS-DRV decreased to less than 1.

# 5. Measurement Results

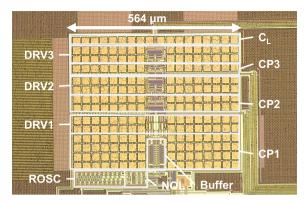

We fabricated a proof-of-concept chip of our proposed ELV-CP and MS-DRV using a 180-nm, 1-poly, 6-metal CMOS technology with a deep n-well option. Figure 13 shows a micrograph of our chip. The area including our proposed ELV-CP, MS-DRV, and peripheral circuits, is 0.36 mm<sup>2</sup>.

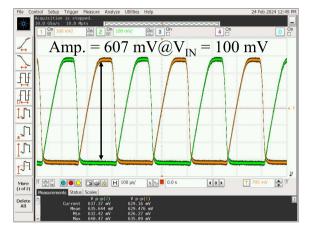

Figure 14 shows the measured waveform of the MS-

Fig. 13 Chip micrograph.

Fig. 14 Measured waveform of the MS-DRV at  $V_{\rm IN}$  = 100 mV.

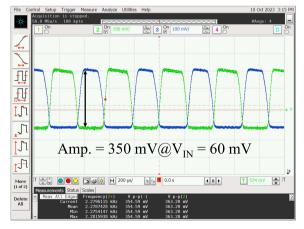

Fig. 15 Measured waveform of the MS-DRV at  $V_{IN} = 60 \text{ mV}$ .

DRV when the  $V_{\rm IN}=100$  mV. In this measurement, we used a mixed signal oscilloscope (Keysight: MSO9254A) and on-chip source follower buffers to drive the parasitic resistance and capacitance. As can be seen, we obtained two non-overlapping clock signals with enough NOL period. The amplitude of the output signals of the MS-DRV was 607 mV. Figure 15 shows the measured waveform when the  $V_{\rm IN}=60$  mV. We confirmed the low-voltage operation of the MS-

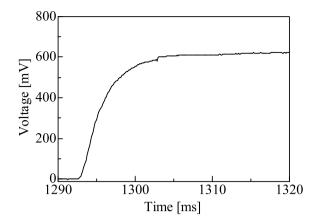

Fig. 16 Measured output voltage waveform.

Fig. 17 Measured output voltages at different  $V_{\rm IN}s$  as a function of load current.

DRV. The amplitude of the output signals was 350 mV.

Figure 16 shows the measured output voltage of the ELV-CP. In the measurement, we applied a pulse voltage to the input and monitored the output voltage by the semiconductor device parameter analyzer (Keysight: B1500A). The amplitude of the input voltage was set to 100 mV. The output voltage was settled to 620 mV with a 11-ms settling time. The measured output voltage was lower than that of the simulation. The reason for this could be the process variation and leakage current of MOSFETs. As shown in Fig. 12, the simulated VCR decreased as the threshold voltage decreased. Therefore, the threshold voltage condition in our chip might be lower than the TT condition, resulting in the output voltage reduction. The settling time was longer than that of the simulated one. This was because the clock frequency of the ROSC was lower than expected.

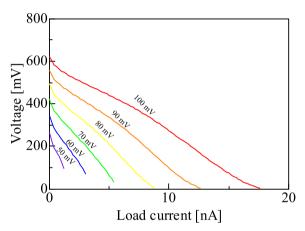

Figure 17 shows the measured load-current dependence of the output voltage of the ELV-CP when the  $V_{\rm IN}$  was set to 50 to 100 mV. The output voltage decreased as the load current increased. The lower the  $V_{\rm IN}$ , the narrower the output current range. This is because the input power and the frequency of the ROSC decreased as the  $V_{\rm IN}$  decreased.

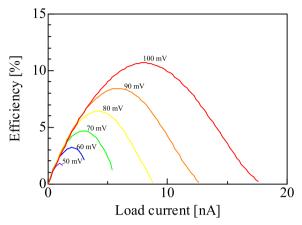

Figure 18 shows the measured power conversion effi-

ciency of the ELV-CP when the  $V_{\rm IN}$  was set to 50 to 100 mV. The maximum efficiency was 10.7% at  $V_{\rm IN}=100$  mV and  $I_{\rm load}=8.0$  nA. The efficiency also degraded as the sim-

Fig. 18 Measured PCEs at different  $V_{\rm IN}$ s as a function of load current.

Fig. 19 Measured and simulated VCRs as a function of input voltage. 10 chips were measured in total.

Table 1

Number of chips among 10 chips that operated at given  $V_{IN}$ .

|                      |    | r  |    | -6 |    |    |    | 8  | . 114 |

|----------------------|----|----|----|----|----|----|----|----|-------|

| V <sub>IN</sub> [mV] | 45 | 46 | 47 | 48 | 49 | 50 | 55 | 56 | 57    |

| Count                | 0  | 0  | 1  | 5  | 8  | 8  | 9  | 10 | 10    |

ulated results. We consider the difference came from the process variation and parasitic loss. As shown in Fig. 11, the PCEs at FF corner were lower than those at TT corner. As discussed in Fig. 16, the threshold voltage in our chip might be slightly lower than the TT condition. In addition, we obtained Fig. 11 by SPICE simulation. The parasitic loss was no taken into consideration. Therefore, the PCEs were lower than the simulated results.

Figure 19 shows the measured VCRs of the ELV-CP as a function of the input voltage. The results for 10 sample chips were depicted. The simulation results were also plotted for comparison. All 10 chips achieved the VCR above 6 at  $V_{\rm IN}=100$  mV. The VCR degraded compared to the simulated one. This was because of the process variation and parasitic capacitance.

Table 1 gives the measured number of chips that operated successfully at different  $V_{\rm IN}$ s. We counted the number of chips when the VCR exceeds 4 at given  $V_{\rm IN}$ . All chips operated successfully with  $V_{\rm IN}$  above 56 mV. Even though the voltage was slightly higher than that of simulation results, our proposed circuit achieved extremely low cold-start voltage.

Table 2 summarizes a performance summary and comparison of our proposed circuit and others [16]–[19], [21], [27], [32]. In the table, we used "settling time" for the charge pump circuits and "startup time" for the boost converters, because the charge pump circuit is part of the boost converter. All circuits demonstrate low cold-start voltages. However, [19] is relatively high cold-start voltage compared with others, and [21], [27] need an off-chip external clock signal. Our proposed fully-integrated circuit achieved comparable cold-start voltages to others [16]–[18], [32] with the fastest settling time. Thus, our proposed circuit is efficient and useful for low-voltage thermometric energy harvesting systems.

## 6. Conclusion

Capable of extremely low-voltage operation for sub-60-mV energy-harvesting applications, an extremely low-voltage charge pump (ELV-CP) and its dedicated multi-stage driver (MS-DRV) were proposed. Although the proposed ELV-CP

Table 2

Performance summary and comparison.

| Parameter                  | This work     | [21]             | [27]             | [17]                  | [18]                  | [16]          | [19]         | [32]           |

|----------------------------|---------------|------------------|------------------|-----------------------|-----------------------|---------------|--------------|----------------|

| Technology                 | 180 nm        | 28 nm            | 350 nm           | 180 nm                | 180 nm                | 180 nm        | 65 nm        | 55 nm          |

| Type                       | CP 1)         | CP 1)            | CP 1)            | CP + PG <sup>2)</sup> | CP + PG <sup>2)</sup> | BC 3)         | BC 3)        | BC 3)          |

| Cold-start<br>voltage (mV) | 56            | 50               | 80               | 57                    | 60                    | 50            | 210          | 83             |

| Cold-start integration     | Yes           | No<br>(Ext. CLK) | No<br>(Ext. CLK) | Yes                   | Yes                   | Yes           | Yes          | Yes            |

| Settling time (ms)         | 11<br>@100 mV | 0.4<br>@50 mV    | _                | _                     | _                     | _             | _            | _              |

| Startup time (ms)          | _             | _                | _                | 135<br>@57 mV         | 20<br>@60 mV          | 21<br>@100 mV | 11<br>@68 mV | 5000<br>@83 mV |

| Area (mm <sup>2</sup> )    | 0.36          | 0.012            | 0.51             | 0.96                  | 0.42                  | 1.02          | 4.6          | 2.6            |

and driver are based on conventional ones, they are modified so that the output voltage of the proposed MS-DRV is maximized. The proposed MS-DRV utilizes the output voltages of each stage of the CP to efficiently boost the control signals. The boosted control clock signals are used as switching signals for each CP and DRV to turn the switch transistors on or off. Moreover, reset transistors are added to the DRV to ensure an adequate non-overlapping period between switching signals. Measured results demonstrated that the proposed MS-DRV can generate boosted clock signals of 350 mV from input voltage of 60 mV. The ELV-CP can boost the input voltage of 100 mV with 10.7% peak efficiency at  $I_{\rm load} = 8.0$  nA. The proposed CP and DRV can boost the low input voltage of 56 mV.

## Acknowledgments

This work was supported through the activities of VDEC, the University of Tokyo, in collaboration with Cadence Design Systems and Mentor Graphics. This work was also partly supported by JSPS KAKENHI Grant Numbers JP20H00606, JP22H03558, JP23H03364, and JP23KJ1425.

## References

- [1] S. Bandyopadhyay, P.P. Mercier, A.C. Lysaght, K.M. Stankovic, and A.P. Chandrakasan, "A 1.1 nW Energy-Harvesting System with 544 pW Quiescent Power for Next-Generation Implants," IEEE J. Solid-State Circuits, vol.49, no.12, pp.2812–2824, Dec. 2014. DOI: 10.1109/JSSC.2014.2350260

- [2] T. Ozaki, T. Hirose, H. Asano, N. Kuroki, and M. Numa, "Fully-Integrated High-Conversion-Ratio Dual-Output Voltage Boost Converter With MPPT for Low-Voltage Energy Harvesting," IEEE J. Solid-State Circuits, vol.51, no.10, pp.2398–2407, Oct. 2016. DOI: 10.1109/JSSC.2016.2582857

- [3] J. Katic, S. Rodriguez, and A. Rusu, "A Dual-Output Thermoelectric Energy Harvesting Interface With 86.6% Peak Efficiency at 30 μW and Total Control Power of 160 nW," IEEE J. Solid-State Circuits, vol.51, no.8, pp.1928–1937, Aug. 2016. DOI: 10.1109/JSSC.2016.2561959

- [4] M.-J. Chung, T. Hirose, T. Ono, and P.-H. Chen, "A 115x Conversion-Ratio Thermoelectric Energy-Harvesting Battery Charger for the Internet of Things," IEEE Trans. Circuits and Syst. I, Reg. Papers, vol.67, no.11, pp.4110–4121, 2020. DOI: 10.1109/TCSI.2020.3012599

- [5] E.J. Carlson, K. Strunz, and B.P. Otis, "A 20 mV Input Boost Converter With Efficient Digital Control for Thermoelectric Energy Harvesting," IEEE J. Solid-State Circuits, vol.45, no.4, pp.741–750, April 2010. DOI: 10.1109/JSSC.2010.2042251

- [6] Z. Shang, Y. Zhao, W. Gou, L. Geng, and Y. Lian, "83.9% Efficiency 100-mV Self-Startup Boost Converter for Thermoelectric Energy Harvester in IoT Applications," IEEE Trans. Circuits and Syst. II, Exp. Briefs, vol.67, no.9, pp.1654–1658, Sept. 2020. DOI: 10.1109/TCSII.2020.2999331

- [7] S.S. Amin and P.P. Mercier, "MISIMO: A Multi-Input Single-Inductor Multi-Output Energy Harvesting Platform in 28-nm FD-SOI for Powering Net-Zero-Energy Systems," IEEE J. Solid-State Circuits, vol.53, no.12, pp.3407–3419, Dec. 2018. DOI: 10.1109/JSSC.2018.2865467

- [8] Y. Xing and L. Liu, "A 10mV Input, 93.6% Peak Efficiency Three-mode Boost Converter for Thermoelectric Energy Harvesting," IEEE 15th International Conference on Solid-State & Integrated Circuit Technology, pp.1–3, 2020. DOI: 10.1109/IC-

#### SICT49897.2020.9278268

- [9] T. Ozaki, T. Hirose, T. Nagai, K. Tsubaki, N. Kuroki, and M. Numa, "A highly efficient switched-capacitor voltage boost converter with nano-watt MPPT controller for low-voltage energy harvesting," IEICE Trans. Fundam. Electron. Commun. Comput. Sci., vol.E99-A, no.12, pp.2491–2499, 2016. DOI: 10.1587/transfun.E99.A.2491

- [10] R. Pelliconi, D. Iezzi, A. Baroni, M. Pasotti, and P.L. Rolandi, "Power efficient charge pump in deep submicron standard CMOS technology," IEEE J. Soid-State Circuits, vol.38, no.6, pp.1068–1071, June 2003.

- [11] J.F. Dickson, "On-chip high-voltage generation in MNOS integrated circuits using an improved voltage multiplier technique," IEEE J. Solid-State Circuits, vol.11, no.3, pp.374–378, June 1976. DOI: 10.1109/JSSC.1976.1050739

- [12] T. Hirose and Y. Nakazawa, "Design of switched-capacitor voltage boost converter for low-voltage and low-power energy harvesting systems," IEICE Trans. Electron., vol.E103-C, no.10, pp.446–457, 2020. DOI: 10.1587/transele.2019CTI0002

- [13] J. Mu and L. Liu, "A 12 mV Input, 90.8% Peak Efficiency CRM Boost Converter With a Sub-Threshold Startup Voltage for TEG Energy Harvesting," IEEE Trans. Circuits and Syst. I, Reg. Papers, vol.65, no.8, pp.2631–2640, Aug. 2018. DOI: 10.1109/TCSI.2018.2789449

- [14] R.L. Radin, M. Sawan, C. Galup-Montoro, and M.C. Schneider, "A 7.5-mV-Input Boost Converter for Thermal Energy Harvesting With 11-mV Self-Startup," IEEE Trans. Circuits and Syst. II, Exp. Briefs, vol.67, no.8, pp.1379–1383, Aug. 2020. DOI: 10.1109/TC-SII.2019.2939123

- [15] P.-S. Weng, H.-Y. Tang, P.-C. Ku, and L.-H. Lu, "50 mV-Input Batteryless Boost Converter for Thermal Energy Harvesting," IEEE J. Solid-State Circuits, vol.48, no.4, pp.1031–1041, April 2013. DOI: 10.1109/JSSC.2013.2237998

- [16] S. Bose, T. Anand, and M.L. Johnston, "A 3.5-mV Input Single-Inductor Self-Starting Boost Converter With Loss-Aware MPPT for Efficient Autonomous Body-Heat Energy Harvesting," IEEE J. Solid-State Circuits, vol.56, no.6, pp.1837–1848, June 2021. DOI: 10.1109/JSSC.2020.3042962

- [17] S. Bose, T. Anand, and M.L. Johnston, "Integrated Cold Start of a Boost Converter at 57 mV Using Cross-Coupled Complementary Charge Pumps and Ultra-Low-Voltage Ring Oscillator," IEEE J. Solid-State Circuits, vol.54, no.10, pp.2867–2878, Oct. 2019. DOI: 10.1109/JSSC.2019.2930911

- [18] M. Coustans, F. Krummenacher, and M. Kayal, "A Fully Integrated 60 mV Cold-Start Circuit for Single Coil DC–DC Boost Converter for Thermoelectric Energy Harvesting," IEEE Trans. Circuits and Syst. II, Exp. Briefs, vol.66, no.10, pp.1668–1672, Oct. 2019. DOI: 10.1109/TCSII.2019.2922683

- [19] Z. Luo, L. Zeng, B. Lau, Y. Lian, and C.-H. Heng, "A Sub-10 mV Power Converter With Fully Integrated Self-Start, MPPT, and ZCS Control for Thermoelectric Energy Harvesting," IEEE Trans. Circuits and Syst. I, Reg. Papers, vol.65, no.5, pp.1744–1757, May 2018. DOI: 10.1109/TCSI.2017.2757505

- [20] P. Chen, K. Ishida, K. Ikeuchi, X. Zhang, K. HOnda, Y. OKuma, Y. Ryu, M. Takamiya, and T. Sakurai, "Startup Techniques for 95 mV Step-Up Converter by Capacitor Pass-On Scheme and V<sub>TH</sub>-Tuned Oscillator With Fixed Charge Programming," IEEE J. Solid-State Circuits, vol.47, no.5, pp.1252–1260, May 2012. DOI: 10.1109/JSSC.2012.2185589

- [21] A. Ballo, A.D. Grasso, and G. Palumbo, "A Subthreshold Cross-Coupled Hybrid Charge Pump for 50-mV Cold-Start," IEEE Access, vol.8, pp.188959–188969, 2020. DOI: 10.1109/AC-CESS.2020.3032452

- [22] J.-T. Wu and K.-L. Chang, "MOS charge pumps for low-voltage operation," IEEE J. Soid-State Circuits, vol.33, no.4, pp.592–597, April 1998, DOI: 10.1109/4.663564

- [23] T. Yim, S. Lee, C. Lee, and H. Yoon, "A Low-Voltage Charge Pump with High Pumping Efficiency," IEEE Region 10 Conference, pp.2135–2139, 2018. DOI: 10.1109/TENCON.2018.8650247

- [24] H. Sebe, D. Kanemoto, and T. Hirose, "Sub-50-mV Charge Pump and its Driver for Extremely Low-Voltage Thermal Energy Harvesting," IEEE Int. Symp. on Circuits and Systems, pp.2773–2777, 2022. DOI: 10.1109/ISCAS48785.2022.9937304

- [25] Y. Tsuji, T. Hirose, T. Ozaki, H. Asano, N. Kuroki, and M. Numa, "A 0.1-0.6 V input range voltage boost converter with low-leakage driver for low-voltage energy harvesting," IEEE Int. Conf. Electron., Circuits Syst., pp.502–505, 2017. DOI: 10.1109/ICECS.2017.8292004

- [26] M. Nishi, Y. Nakazawa, K. Matsumoto, N. Kuroki, M. Numa, R. Matsuzuka, O. Maida, D. Kanemoto, and T. Hirose, "Sub-0.1V Input, Low-Voltage CMOS Driver Circuit for Multi-Stage Switched Capacitor Voltage Boost Converter," IEEE Int. Conf. Electron., Circuits Syst., pp.530–533, 2019. DOI: 10.1109/ICECS46596.2019.8964719

- [27] C.-Y. Tsui, H. Shao, W.-H. Ki, and F. Su, "Ultra-low voltage power management circuit and computation methodology for energy harvesting applications," Asia and South Pacific Conf. on Design Automation, pp.96–97, 2006. DOI: 10.1109/ASPDAC.2006.1594654

- [28] S. Bose and M.L. Johnston, "A Stacked-Inverter Ring Oscillator for 50 mV Fully-Integrated Cold-Start of Energy Harvesters," IEEE Int. Symp. Circuits and Syst., pp.1–5, 2018. DOI: 10.1109/IS-CAS.2018.8351445

- [29] M. Nishi, K. Matsumoto, N. Kuroki, M. Numa, H. Sebe, R. Matsuzuka, O. Maida, D. Kanemoto, and T. Hirose, "A 35-mV supply ring oscillator consisting of stacked body bias Inverters for extremely low-voltage LSIs," IEICE Electron. Exp., vol.18, no.6, 20210065, 2021. DOI: 10.1587/elex.18.20210065

- [30] R. Matsuzuka, T. Terada, K. Matsumoto, M. Kitamura, and T. Hirose, "A 42-mV startup ring oscillator using gain-enhanced self-bias inverters for extremely low voltage energy harvesting," Jpn. J. Appl. Phys., vol.59, SGGL01, 2020. DOI: 10.7567/1347-4065/ab65d4

- [31] H. Sebe, K. Matsumoto, R. Matsuzuka, O. Maida, D. Kanemoto, and T. Hirose, "A self-bias NAND gate and its application to nonoverlapping clock generator for extremely low-voltage CMOS LSIs," Jpn. J. Appl. Phys., vol.60, SBBL06, 2021. DOI: 10.35848/1347-4065/abeac2

- [32] J. Tao, W. Mao, Z. Luo, L. Zeng, and C.-H. Heng, "A Fully Integrated Power Converter for Thermoelectric Energy Harvesting With 81% Peak Efficiency and 6.4-mV Minimum Input Voltage," IEEE Trans. Power Electronics, vol.37, no.5, pp.4968–4972, May 2022. DOI: 10.1109/TPEL.2021.3134367.

**Hikaru Sebe** recieved the B.S. and M.S. degrees in the Division of Electrical, Electronic and Infocommunications Engineering from Osaka University, Osaka, Japan, in 2020 and 2022, respectively. He is currently working toward the Ph.D. degree at the same university. His current research interests are in ultra-low-power and ultra-low-voltage CMOS circuits design.

Daisuke Kanemoto received the B.S. degree in Electronics and Information Science from Kyoto Institute of Technology, Kyoto, Japan, in 2004 and received the M.S. and Ph.D. degrees in Electronic Engineering from Osaka University, Osaka, Japan, in 2006, 2011. From November 2010, he was an assistant professor at the Department of Electronics, Graduate School of Information Science and Electrical Engineering, Kyushu University, Fukuoka, Japan. From April 2013, he was an assistant professor at the De-

partment of Research Interdisciplinary Graduate School of Medicine and Engineering, University of Yamanashi, Yamanashi, Japan. From May 2015, he was a visiting assistant professor at the Department of Electrical Engineering, Stanford University, Stanford, USA. From June 2019, he has been an associate professor at the Graduate School of Engineering Osaka University, Osaka, Japan. His research interests include analog circuits, mixed-signal integrated circuits and compressed sensing. He is an IEEE member.

Tetsuya Hirose received B.S., M.S., and Ph.D. degrees from Osaka University, Osaka, Japan, in 2000, 2002, and 2005, respectively. From 2004 to 2008, he was a Research Associate with the Department of Electrical Engineering, Hokkaido University, Sapporo, Japan. From 2008 to 2019, he was an Associate Professor with the Department of Electrical and Electronics Engineering, Kobe University, Kobe, Japan. Since 2019, he has been a Professor with the Division of Electrical, Electronic and Information Engi-

neering, Graduate School of Engineering, Osaka University, Suita, Japan. He has authored or co-authored over 200 journal and conference papers. His current research interests are extremely low-voltage and low-power analog/digital mixed-signal integrated circuit design and smart sensor systems. Dr. Hirose is a senior member of the Institute of Electrical and Electronics Engineers (IEEE), and a member of the Institute of Electronics, Information and Communication Engineers (IEICE), and the Japan Society of Applied Physics (JSAP). He was a recipient or co-recipient of the 10th Joint Research Award of the Semiconductor Technology Academic Research Center (STARC) in 2013, the Marubun Research Encouragement Awards in 2017, the IEICE Best Invited Paper Award in 2022, and more than 30 other international and domestic awards. He served as a Technical Program Committee Member of the International Conference on Solid-State Devices and Materials from 2010 to 2013, the Asian Solid-State Circuits Conference from 2011 to 2022, an Associate Editor for the IEICE Electronics Express from 2012 to 2015, the Chapter Secretary of the IEEE SSCS Kansai Chapter from 2015 to 2016, and a Guest Associate Editor for the special issues of IEICE Transactions on Fundamentals of Electronics, Communications and Computer Sciences and on Electronics from 2010 to 2023