## on Electronics

DOI:10.1587/transele.2023ECP5045

Publicized: 2024/04/10

This advance publication article will be replaced by the finalized version after proofreading. **PAPER**

# Measuring SET Pulse Widths in pMOSFETs and nMOSFETs Separately by Heavy-ion and Neutron Irradiation

Jun FURUTA<sup>†</sup>, Member, Shotaro SUGITANI<sup>†</sup>, Ryuichi NAKAJIMA<sup>†</sup>, Student Members, Takafumi ITO<sup>†</sup>, Nonmember, and Kazutoshi KOBAYASHI<sup>†</sup>, Senior Member

**SUMMARY** Radiation-induced temporal errors become a significant issue for circuit reliability. We measured the pulse widths of radiation-induced single event transients (SETs) from pMOSFETs and nMOSFETs separately. Test results show that heavy-ion induced SET rates of nMOSFETs were twice as high as those of pMOSFETs and that neutron-induced SETs occurred only in nMOSFETs. It was confirmed that the SET distribution from inverter chains can be estimated using the SET distribution from pMOSFETs and nMOSFETs by considering the difference in load capacitance of the measurement circuits.

key words: Single Event Transient, Pulse Width, Heavy Ion, High Energy Neutron

#### 1. Introduction

Single event effects are one of a significant issue for circuit reliability since they transiently flip the output of transistor, resulting in circuit malfunction. This malfunction is called soft error [1]–[4]. Single event effects are caused by a charged particle. A charged particle generates electron-hole pairs in semiconductor along its track and the generated electrons are collected to the diffusion region of off-state nMOSFET by the electric field in the depletion layer. Thereby, the output of the off-state nMOSFET is flipped transiently. When a charged particle passes through a logic circuit, its output is inverted for a time depending on the amount of collected charge, which is called single event transient (SET). When a charged particle passes through a storage element, its stored data can be flipped by collected charge, which is called single event upset (SEU). The SEU is more critical to the circuit reliability because incorrect outputs due to SET can only lead to malfunctions when they are captured by flip-flops (FFs). However, SET is more frequently captured by FFs as the clock frequency increases [5], [6]. Therefore, in advanced technology, measuring SET rates and their pulse widths has become important for calculating the soft error rate and estimating the reduction of error rate by low-pass filters [7], [8]. Furthermore, measuring the SET pulse width distribution can be used to evaluate the distribution of the amount of collected charge generated by radiation strike, since the SET pulse width depends on the amount of collected charge.

Previous researches on SETs have reported numerous characteristics, such as temperature characteristics, dependence on well contact density, driving strength and logic

$^\dagger$ Graduate School of Science and Technology, Kyoto Institute of Technology, Japan

circuit structure [9]-[14]. However, most of these studies measured SET pulse widths using CMOS inverter chains. Hence, it is impossible to determine whether the measured SET was generated from an nMOSFET or a pMOSFET. Since the electrons and holes generated by a radiation strike are collected by nMOSFETs and pMOSFETs, respectively, the SETs produced in nMOSFETs can have different characteristics from those in pMOSFETs. Therefore, separated measurement of SETs from nMOSFETs and from pMOS-FETs is important to obtain detailed characteristics of single event transients. To address the above problem, S. Jagannathan et al. measured SET pulse widths from nMOSFET and pMOSFET using partially-duplicated logic chains [12]. Their results showed that pMOSFET had 3.9 times more SETs than nMOSFET. However, only a few reports have measured SET pulse widths using this method.

In addition to a lack of distinction between SETs from nMOSFET and pMOSFET, there were issues with the measurement accuracy of SET pulse width [15]–[17]. SET pulse width can be modulated during propagation through logic gates since SET pulse widths are generally measured using a long logic chain [18]. This propagation-induced pulse modulation (shrinking / broadening) is caused by the difference between the rise and fall propagation times. Thus, the target logic structures need to be considered to achieve high measurement accuracy of SET pulse widths. Additionally, it is crucial to measure the same SET characteristics using different measurement circuits in order to verify the SET characteristics that depend on specific circuit structures.

In this paper, SET pulses widths from nMOSFET (nSET pulse widths) and pMOSFET (pSET pulse widths) were measured to separate single event effects on nMOS-FET and pMOSFET. We show that the impact of singleevent effects is different for nMOSFETs and pMOSFETs by performing the above measurements, indicating that separate measurements are essential for accurate SET modeling and estimating the soft error rate of a circuit. In addition, we clarify the effects of the differences in the measurement circuits by comparing the measurement results of nSETs and pSETs with SET pulse widths measured by the conventional method using inverter chains. The rest of this paper is organized as follows. Section 2 introduces structures of Target logic circuits and time-to-digital converter. The measurement results by Kr ions and neutron irradiation are shown in Section 3. We conclude this paper in Section 4.

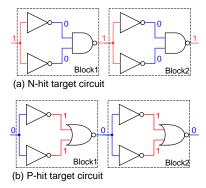

**Fig. 1** Schematics of two of the blocks of (a) N-hit target circuit and (b) P-hit target circuit proposed by S. Jagannathan et al [12].

#### 2. SET Pulse Width Measurement Structures

#### 2.1 Conventional Measurement Structures

Typically, SET pulse widths are measured by a logic gate chain and a time-to-digital converter (TDC) such as vernier delay line [19], [20]. When a SET pulse is generated by radiation passing through one logic gate, the SET propagates through the logic gate chain and is input to the TDC. Thus, SET pulse width can be measured by storing the SET pulse width as a digital signal. The more the number of stages in the logic gate chain under measurement, the more area-efficient the measurement can achieve.

Fig. 1 shows target logic chains to measure nSET and pSET separately, which was proposed by S. Jagannathan et al. Since the inverters are duplicated, a SET generated on the inverters does not change output of NOR gate or NAND gate. Thereby, SETs generated on off-state nMOSFETs in NAND gates are only measured by the N-hit target circuit, and we can measure nSETs and pSETs separately.

SET pulse width measurement using a logic gate chain has a problem due to propagation-induced pulse modulation (PIPM) effect [15]. Because of the difference in propagation delay time of the logic circuit between rising and falling signals, the pulse width increases or decreases linearly as the SET pulse passes through the logic circuit. Thus, the SET pulse width depends on the position in the logic gate chain through which the radiation passes. PIPM effects can occur even in inverter chains due to negative bias temperature instability (NBTI) [17], and it is particularly significant in logic circuits with different even and odd numbered stages, as in the block in Fig. 1. To reduce the PIPM effect, short logic gate chains connected to the inputs of a multi-input OR gate are used for the measurement target.

#### 2.2 Target Structures

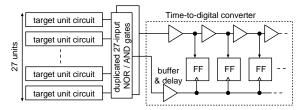

SET pulse width measurement circuits were implemented in a 65 nm bulk process. Their simplified schematic is shown in Fig. 2. It consists of 27 unit circuits as the SET source,

Fig. 2 Simplified schematic diagram of SET pulse width measurement circuit.

duplicated 27-input NOR (or AND) gates and a time-to-digital converter (TDC). In this circuit, the output inversion of an unit circuit caused by a SET is transmitted to inputs of the TDC by the 27-input NOR gates, and the pulse width is saved as a digital signal by the TDC.

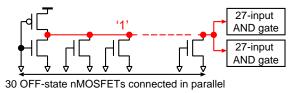

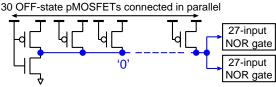

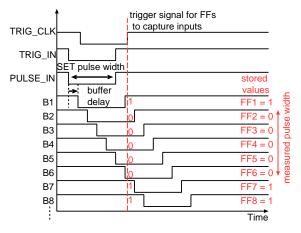

Fig. 3 shows the target unit structures used to measure nSET widths, pSET widths and SET widths from the inverters. Fig. 3 (a) and (b) are based on victim circuit structures reported in Ref. [21]. The structure for nSET was composed of one on-state pMOSFET and 30 off-state nMOSFETs connected in parallel. In this structure, only SET pulses from nMOSFETs were measured because single event effect is caused on off-state MOSFETs. Additionally, the SET pulse width does not change unintentionally by PIPM effect, therefore, SET pulse widths from nMOSFET and pMOSFET can be measured accurately and individually using the unit structures as shown in Fig. 3 (a) and (b). Furthermore, all target unit structures contain an equal number of off-state MOS-FETs, so the area efficiency of the measurement circuit does not decrease when nSETs and pSETs are measured separately.

The SETs from the inverter chain (SET<sub>inv</sub>) cannot separate nSETs and pSETs because the inverter chain contains 15 off-state pMOSFETs and 15 off-state nMOSFETs. SET<sub>inv</sub> were measured for comparison with SETs calculated using nSETs and pSETs obtained from the circuits in Fig. 3 (a) and (b), respectively.

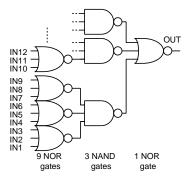

Fig. 4 shows the structure of the 27-input NOR gate. It consists of 3-input NOR gates and 3-input NAND gates to reduce fanout less than four.

#### 2.3 Time-to-digital Converter

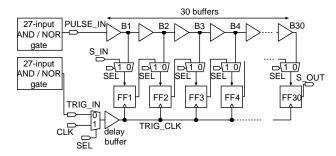

The TDC was implemented based on a snapshot circuit introduced in Ref. [11]. Fig. 5 shows a detailed schematic diagram of the implemented TDC. Fig. 6 shows timing chart of the TDC when a SET is simultaneously input to the two input ports, PULSE\_IN and TRIG\_IN. Input pulse width can be calculated by multiplying the delay time of the buffer and the number of positive-edge triggered FFs that capture flipped output values of the buffers. Measured SET pulse width is stored in the FFs as a sequence of '0'.

The TDC has two input ports to measure pulse width, PULSE\_IN is for the input of the pulse to be measured, and TRIG\_IN is used as a trigger to save the output values of the buffers. The pulse width is not stored unless the SET pulse is simultaneously propagated to the two input ports.

#### (a) unit structure for nSET

#### (b) unit structure for pSET

(15 OFF-state nMOSFETs and 15 OFF-state pMOSFETs)

#### (C) inverter chain

Fig. 3 Schematic diagrams of target unit circuits.

Fig. 4 The structure of the implemented 27-input NOR gate.

Therefore, SETs caused in the TDC and the 27-input NOR / AND gates were not captured by FFs, and SETs caused in the target unit circuits are only measured and stored by the TDC. Therefore, the TDC does not need to be duplicated and achieves better area efficiency than conventional TDCs for SET pulse width measurement.

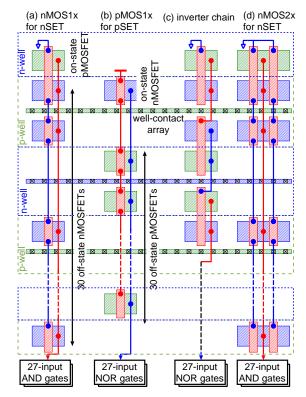

#### 2.4 Fabricated Test Chip

150 SET pulse width measurement circuits were implemented in a 65 nm twin-well bulk process. We implemented single-finger (1x) and two-finger (2x) transistors versions of the three circuits shown in Fig. 3 as the evaluation targets. Two-finger transistors duplicate on-current, while the drain area is quite similar to that of a single-finger transistor. The gate widths of the nMOSFETs and pMOSFETs in Fig. 3 (a) - (c) are 390 nm and 520 nm per finger, respectively. The gate width ratio between pMOSFETs and nMOSFETs is 1.33,

**Fig. 5** Detailed schematic diagram of the implemented TDC. 31 multiplexers are inserted to perform 30 stage shift register which is used to initialize the TDC and to read the measurement.

**Fig. 6** Timing chart of the TDC when a SET is simultaneously input to the two input ports, PULSE\_IN and TRIG\_IN. The delay time of the multiplexers and the setup time of the FFs are ignored in this timing chart.

which is determined by optimizing the delay time and area in the standard cell library [22].

The simplified layouts of the implemented target circuits are partially shown in Fig. 7. Since there are 30 off-state MOSFETs in Fig. 3 (a) and (b), it is possible that a charged particle may affect multiple off-state MOSFETs at the same time. This phenomenon is called charge sharing or multiplenode charge collection [23]. Charge collection in multiple MOSFET connected in parallel can increase the SET pulse width significantly, making it impossible to measure SET pulse widths from a MOSFET. To mitigate this problem, only two off-state MOSFETs in the unit circuit were placed in the same well and an array of well-contacts were inserted between them to suppress multiple-node charge collection and parasitic bipolar effect. Additionally, the unit circuits are placed 1  $\mu$ m from each other to avoid charge sharing between the two unit circuits and to prevent two SET pulses from occurring simultaneously [24].

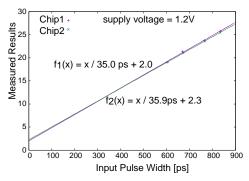

Fig. 8 shows calibration results of the fabricated TDCs in different chips by inputting square wave from a variable-stage ring oscillator and frequency divider circuit. The generated square wave was input to first stage of a 30-stage inverter chain. In this calibration, it was not possible to check the TDC operation using pulses of under 600 ps. However,

**Fig. 7** Simplified layouts of target unit structures: (a) unit structure for nSET with one finger, (b) unit structure for pSET with one finger, (c) inverter chain with one finger and (d) unit structure for nSET with two fingers.

Fig. 8 Calibration results of the implemented TDCs.

resolution of the TDC determined by the delay time of the 30 buffers which does not differ significantly from buffer to buffer. Moreover, the calibration results agreed well with circuit-level simulation results. The resolution of the TDCs was about 35 ps when supply voltage was 1.2 V, which is less than 10% error from the value obtained by the circuit-level simulation. Therefore, we estimate that the TDC maintains a resolution of 35 ps even with input pulses below 600 ps.

#### 3. Experiment Results

### 3.1 Experiment Setup

Heavy ion tests were performed at Cyclotron and Radioiso-

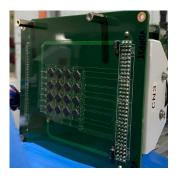

**Fig. 9** Simultaneous measurement of 32 test chips using two PCB boards in the neutron irradiation test.

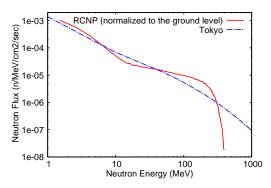

Fig. 10 Neutron spectrum at Tokyo and that from spallation neutron source at RCNP.

tope Center (CYRIC), Tohoku University, Japan. The chip was irradiated perpendicularly with <sup>84</sup>Kr<sup>17+</sup>. The energy and linear energy transfer (LET) values of the Kr ions are 322 MeV and 40 MeVcm<sup>2</sup>/mg. Total fluence of the Kr ions was about 8,000,000 ions/cm<sup>2</sup>.

The flux of heavy ions varies greatly with position in space. Therefore, the probability of heavy-ion-induced SETs is generally expressed using the cross-section (CS) calculated from the following equation [25].

$$CS[\text{cm}^2/\text{target}] = \frac{N_{\text{SET}}}{F_{\text{ION}} \times N_{\text{target}}},$$

(1)

where,  $N_{\rm SET}$  is the number of measured SETs,  $F_{\rm ION}$  is ion fluence per cm<sup>2</sup>,  $N_{\rm target}$  is the number of measurement target (off-state nMOSFETs, pMOSFETs or inverters).

High energy neutron tests using spallation neutron source were performed at Research Center for Nuclear Physics (RCNP), Osaka University, Japan. Fig. 10 shows neutron spectrum at Tokyo and that from spallation neutron source at RCNP. In order to observe as many SET pulses as possible, two test boards with 16 chips each (32 in total) were measured simultaneously (Fig. 9). Chips were tested to a total fluence of  $5 \times 10^9$  n/cm², which is equivalent to the total fluence of neutrons in 400,000 years at ground level (terrestrial neutron flux = 12.9 n/cm²/hr [26]). The probability of neutron-induced SETs is expressed using failure in time (FIT) rate. FIT rate is the number of SETs that can be expected in  $10^9$  hours.

Fig. 11 Distribution of nSET pulse widths by Kr-ion irradiation.

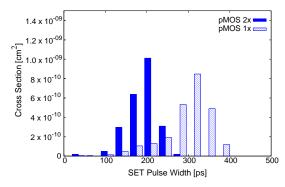

Fig. 12 Distribution of pSET pulse widths by Kr-ion irradiation.

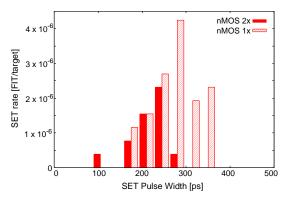

Fig. 13 Distribution of nSET pulse widths by neutron irradiation.

#### 3.2 SET Pulse Widths from pMOSFET and nMOSFET

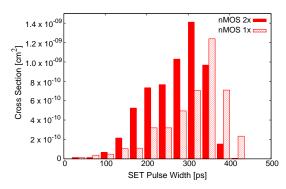

Figs. 11, 12 and 13 show the pulse width distributions of Kr-ion-induced nSET, Kr-ion-induced pSET and neutron-induced nSET, respectively. Since pSET was not induced by neutron tests, only the distribution of nSET pulse widths is shown in Fig. 13. Total number of SETs, total probability of SETs and average SET pulse width are summarized in Tables 1 and 2.

SETs from off-state nMOSFET have larger CS and longer average pulse width than those from off-state pMOSFET. Additionally, there were no pSET events during the neutron tests. These results are due to differences in electron and hole mobility. The electrons that are collected in the off-

state nMOSFET had higher mobility than holes, and more charge is collected in the nMOSFET diffusion region. Furthermore, pMOSFET on-current is smaller than nMOSFET on-current in the measured structures. Thus, longer SETs were more frequently generated from nMOSFETs than from pMOSFETs. The nSETs have a greater impact on circuit reliability than the pSETs, at least when the transistor sizes evaluated in this paper are used in standard cells.

The nSETs and pSETs also have different degrees of dependence on the number of fingers (drive strength). In the Kr-ion tests, increasing the number of fingers reduced the pulse widths of the nSETs and pSETs by 10% and 40%, respectively. It is assumed that the pulse widths of pSETs are reduced by the on-current from nMOSFETs, which doubles with the increase in the number of fingers. In the case of nSETs, the increase in the number of fingers also doubles the on-current from pMOSFETs, but we assume that twice the number of off-state nMOSFETs increases the amount of radiation-induced parasitic bipolar current, so that the effect of twice the on-current from pMOSFETs become smaller [10]. These results are consistent with the fact that the current amplification factor of a lateral npn bipolar transistor is greater than that of a lateral pnp bipolar transistor in the 65 nm process design kit. Based on the above measurements, separate measurements of nSET and pSET are essential in SET modeling because the characteristics of nSET and pSET are different.

In a previous study, pSETs were reported to be approximately 3.9 times higher than nSETs [12], however, this is not consistent with our results. We assume that this is due to the difference in the gate width of the pMOSFETs. In Ref. [12], the gate widths of sensitive pMOSFET and nMOSFET were 1.3  $\mu$ m and 400 nm, respectively, while, in our target circuits they were 520 nm and 390 nm. There is more than twice the difference in the gate width of the pMOSFETs.

In this experiment, we also measured the single event upset (SEU) rates on standard FFs using Kr ions and neu-The CS of Kr-ion-induced SEU rate was 1.50  $\times 10^{-8}$  cm<sup>2</sup>/FF and the neutron-induced SEU rate was 5  $\times$ 10<sup>-4</sup> FIT/FF. Neutron-induced SET rate was about two order of magnitude lower than the SEU rate. In contrast, CS of Kr-ion-induced SET was 1/6 - 1/4 of the SEU rate, which is a significant ratio since combinational circuits are basically composed of a large number of logic circuits. SET protection is also necessary in space where heavy ions exist. As can be inferred from the SEU rates on standard FFs, 851 and 533 SEUs on FFs in the TDC were also observed in the accelerated tests with neutrons and Kr ions, respectively. However, as shown in the calibration results (Fig. 8), SET measurement data is always stored in the FFs as three or more consecutive zeros, making it easily distinguishable from the SEUs.

#### 3.3 nSET and pSETs versus SETs from Inverter Chains

SETs from a 30-stage inverter chain (Fig.3(c)) occur in 15 off-state nMOSFETs and 15 off-state pMOSFETs. Therefore,

Measurement results of SET pulses by Kr-ions irradiation. Table 1

|         |        | total number | total CS of SETs          | avg. SET   |

|---------|--------|--------------|---------------------------|------------|

| target  | finger | of SETs      | [cm <sup>2</sup> /target] | width [ps] |

| nMOSFET | 2x     | 956          | $5.9 \times 10^{-9}$      | 270        |

|         | 1x     | 703          | 4.3 ×10 <sup>-9</sup>     | 310        |

| pMOSFET | 2x     | 382          | $2.4 \times 10^{-9}$      | 190        |

|         | 1x     | 404          | $2.5 \times 10^{-9}$      | 300        |

Measurement results of SET pulses by neutron irradiation. Table 2

|         |        | total number | total SET rate       | avg. SET   |

|---------|--------|--------------|----------------------|------------|

| target  | finger | of SETs      | [FIT/target]         | width [ps] |

| nMOSFET | 2x     | 14           | $5.4 \times 10^{-6}$ | 150        |

|         | 1x     | 36           | $1.4 \times 10^{-5}$ | 200        |

| pMOSFET | 2x     | 0            | -                    | _          |

|         | 1x     | 0            | _                    | _          |

Table 3 Measurement and calculated results of Kr-ion-induced SETs from inverters.

|                    |        | total number | total CS of SETs          | avg. SET   |

|--------------------|--------|--------------|---------------------------|------------|

|                    | finger | of SETs      | [cm <sup>2</sup> /target] | width [ps] |

| measured           | 2x     | 725          | $4.5 \times 10^{-9}$      | 180        |

| $SET_{inv}$        | 1x     | 711          | $4.4 \times 10^{-9}$      | 160        |

| calculated         | 2x     | _            | $4.2 \times 10^{-9}$      | 250        |

| SET <sub>inv</sub> | 1x     | _            | $3.4 \times 10^{-9}$      | 310        |

Measurement and calculated results of neutron-induced SETs from inverters.

|                    |        | total number | total SET rate       | avg. SET   |

|--------------------|--------|--------------|----------------------|------------|

|                    | finger | of SETs      | [FIT/target]         | width [ps] |

| measured           | 2x     | 4            | $1.5 \times 10^{-6}$ | 40         |

| SET <sub>inv</sub> | 1x     | 13           | $5.0 \times 10^{-6}$ | 80         |

| calculated         | 2x     | _            | $2.7 \times 10^{-6}$ | 150        |

| SET <sub>inv</sub> | 1x     | _            | $7.0 \times 10^{-6}$ | 200        |

the SET cross section and error probability of the inverter chain,  $CS_{inv}$  and  $P_{inv}$  can be calculated from the following equations.

$$CS_{\text{inv}} = \frac{CS_{\text{pSET}} + CS_{\text{nSET}}}{2},$$

$$P_{\text{inv}} = \frac{P_{\text{pSET}} + P_{\text{nSET}}}{2}.$$

(2)

$$P_{\text{inv}} = \frac{P_{\text{pSET}} + P_{\text{nSET}}}{2}.$$

(3)

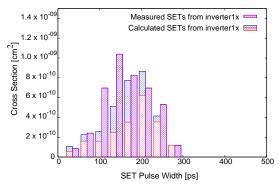

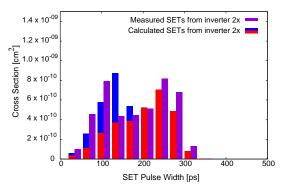

In this section, we compare measured SETs from the inverter chain and SETs calculated from the measurement results of nSET and pSETs.

The measured and calculated SET rates in inverter chain are summarized in Tables 3 and 4. For both neutron and heavy ion tests, the average SET<sub>inv</sub> pulse widths were about 100 ps shorter than the average SET<sub>inv</sub> pulse width calculated by nSET and pSET. There are two possible reasons for this: one is the difference in load capacitance, and the other is multiple node charge collection in the inverter chain. In the nSETs and pSETs measurement circuits, 30 off-state MOSFETs provided a large junction capacitance and load capacitance are several times larger than those in the inverter chain. Thereby, the recovery speed from radiation-induced inversion became slower. The voltage variation due to an ion strike is also slower due to the large load capacitance.

Measured and calculated distribution of SET pulse widths from inverter 1x. Red and blue bars represent nSET and pSET, respectively.

Measured and calculated distribution of SET pulse widths from inverter 2x. Red and blue bars represent nSET and pSET, respectively.

However, compared to the increase in recovery time, the time increase in radiation-induced voltage change is relatively small since the drift current due to a radiation strike has a large peak value [27], [28]. In addition, the drift is effective for a longer time due to the large load capacitance, and more significant charges are collected. longer SET pulses were more likely to occur in the nSETs and pSETs experiment circuits. Another reason could be pulse quenching, which is a reduction of SET pulse widths in the inverter chains due to multiple node charge collection [29]–[31]. Pulse quenching is caused by charge collecting in the on-state MOSFETs and the collected charge suppresses the inversion time (SET pulse width). Additionally, since the charge generated by radiation strikes change the well potential, it increases the on-current of the MOSFET as a forward body bias. Thus, the recovery speed increases from the SET inversion and the SET pulse width shortens. These effects are less likely to occur in nSETs and pSETs measurement circuits because there are only one on-state MOSFET and it is separated from most of the off-state MOSFETs (Fig. 7).

Measured and calculated distributions of the Kr-ioninduced SET<sub>inv</sub> pulse widths are shown in Figs. 14 and 15. The distributions calculated by nSETs and pSETs were adjusted by subtracting the difference in average pulse widths to consider the effects described above. The calculated pulse width distributions were consistent with the measurement results using the inverter chain. In particular, the calculated distribution reproduced the measurement result of two-finger transistors that had two peaks: the peak around 100 ps is composed of nSETs and pSETs, while the other peak is composed of only nSETs (Fig. 15). The above results indicate that the proposed nSET and pSET measurement circuits can be used to analyze SET in inverters. For more accurate measurement, use a circuit that matches the load capacitance of the inverter chain and to consider multiple node charge collection in the inverter chain.

#### 4. Conclusion

SET pulse widths for pMOSFETs were measured separately from those for nMOSFETs in a 65 nm bulk process using off-state pMOSFETs or nMOSFETs connected in parallel. Measurement results show that nMOSFETs had twice the the heavy-ion-induced SET rate as pMOSFETs and neutroninduced SETs were only observed from nMOSFETs. In addition, the nSETs and pSETs also have different degrees of dependence on the number of fingers. In the Kr-ion tests, increasing the number of fingers reduced the pulse widths of the nSETs and pSETs by 10% and 40%, respectively. Based on the above results, separate measurements of nSET and pSET are essential in SET modeling because the characteristics of nSET and pSET are different. On the ground level, it is less effective for circuit reliability to protect pMOSFETs from single event effects when the transistor sizes of the nMOSFET and pMOSFET are roughly equivalent.

This measurement also compared SET from inverter chains with nSETs and pSETs, and observed that nSETs and pSETs had larger average SET pulse width than SET from inverters, due to differences in load capacitance and multi-node charge collection. However, it was confirmed that the peaks in the pulse width distribution of SETs from inverter chains could be reproduced by the pulse width distribution calculated from measurement results of nSETs and pSETs. More accurate nSETs and pSETs measurements can be achieved by reducing the number of MOSFETs connected in parallel, thereby reducing load capacitance. By reducing the load capacitance of the target circuits, the SET distribution of an inverter can be calculated from pSET and nSET without measuring the average SET of an inverter.

#### Acknowledgments

The authors would like to thank to Cyclotron and Radioisotope Center (CYRIC), Tohoku University and Research Center for Nuclear Physics (RCNP), Osaka University for heavy ion and high energy neutron experiments. This work was supported through the activities of VDEC, The University of Tokyo, in collaboration with Cadence Design Systems, NIHON SYNOPSYS G.K. and Siemens Electronic Design Automation Japan K.K..

#### References

[1] T. Karnik and P. Hazucha, "Characterization of soft errors caused

- by single event upsets in CMOS processes," IEEE Transactions on Dependable and Secure Computing, vol.1, no.2, pp.128–143, 2004.

- [2] H. Kobayashi, N. Kawamoto, J. Kase, and K. Shiraish, "Alpha particle and neutron-induced soft error rates and scaling trends in SRAM," IEEE International Reliability Physics Symposium, pp.206–211, 2009.

- [3] N. Seifert, P. Slankard, M. Kirsch, B. Narasimham, V. Zia, C. Brookreson, A. Vo, S. Mitra, B. Gill, and J. Maiz, "Radiationinduced soft error rates of advanced CMOS bulk devices," IEEE International Reliability Physics Symposium, pp.217–225, 2006.

- [4] B. Narasimham, V. Chaudhary, M. Smith, L. Tsau, D. Ball, and B. Bhuva, "Scaling trends in the soft error rate of srams from planar to 5-nm finfet," 2021 IEEE International Reliability Physics Symposium (IRPS), pp.1–5, 2021.

- [5] N.N. Mahatme, I. Chatterjee, B.L. Bhuva, J. Ahlbin, L.W. Massengill, and R. Shuler, "Analysis of soft error rates in combinational and sequential logic and implications of hardening for advanced technologies," IEEE International Reliability Physics Symposium, pp.1031–1035, 2010.

- [6] B. Gill, N. Seifert, and V. Zia, "Comparison of alpha-particle and neutron-induced combinational and sequential logic error rates at the 32nm technology node," IEEE International Reliability Physics Symposium, pp.199–205, 2009.

- [7] P. Eaton, J. Benedetto, D. Mavis, K. Avery, M. Sibley, M. Gadlage, and T. Turflinger, "Single event transient pulsewidth measurements using a variable temporal latch technique," IEEE Transactions on Nuclear Science, vol.51, no.6, pp.3365–3368, 2004.

- [8] E. Keren, S. Greenberg, N.M. Yitzhak, D. David, N. Refaeli, and A. Haran, "Characterization and mitigation of single-event transients in xilinx 45-nm SRAM-based FPGA," IEEE Transactions on Nuclear Science, vol.66, no.6, pp.946–954, 2019.

- [9] M. Gadlage, J. Ahlbin, B. Narasimham, V. Ramachandran, C. Dinkins, N.D. Pate, B. Bhuva, R. Schrimpf, L. Massengill, R. Shuler, and D. McMorrow, "Increased single-event transient pulsewidths in a 90-nm bulk CMOS technology operating at elevated temperatures," IEEE Transactions on Device and Materials Reliability, vol.10, no.1, pp.157–163, 2010.

- [10] J. Furuta, R. Yamamoto, K. Kobayashi, and H. Onodera, "Evaluation of parasitic bipolar effects on neutron-induced SET rates for logic gates," IEEE International Reliability Physics Symposium, pp.SE.5.1–SE.5.5, 2012.

- [11] Y. Yanagawa, K. Hirose, H. Saito, D. Kobayashi, S. Fukuda, S. Ishii, D. Takahashi, K. Yamamoto, and Y. Kuroda, "Direct measurement of SET pulse widths in 0.2- \(\mu\) m soi logic cells irradiated by heavy ions," IEEE Transactions on Nuclear Science, vol.53, no.6, pp.3575–3578, 2006

- [12] S. Jagannathan, M.J. Gadlage, B.L. Bhuva, R.D. Schrimpf, B. Narasimham, J. Chetia, J.R. Ahlbin, and L.W. Massengill, "Independent measurement of set pulse widths from n-hits and p-hits in 65-nm cmos," IEEE Transactions on Nuclear Science, vol.57, no.6, pp.3386–3391, 2010.

- [13] C. Jianjun, C. Shuming, C. Yaqing, and L. Bin, "Characterization of single-event transient pulse quenching among dummy gate isolated logic nodes in 65 nm twin-well and triple-well CMOS technologies," IEEE Transactions on Nuclear Science, vol.62, no.5, pp.2302–2309, 2015

- [14] B. Narasimham, B. Bhuva, R. Schrimpf, L. Massengill, M. Gadlage, W. Holman, A. Witulski, W. Robinson, J. Black, J. Benedetto, and P. Eaton, "Effects of guard bands and well contacts in mitigating long SETs in advanced CMOS processes," 9th European Conference on Radiation and Its Effects on Components and Systems, pp.1–6, 2007.

- [15] V. Ferlet-Cavrois, P. Paillet, D. McMorrow, N. Fel, J. Baggio, S. Girard, O. Duhamel, J.S. Melinger, M. Gaillardin, J.R. Schwank, P.E. Dodd, M.R. Shaneyfelt, and J.A. Felix, "New insights into single event transient propagation in chains of inverters—evidence for propagation-induced pulse broadening," IEEE Transactions on Nuclear Science, vol.54, no.6, pp.2338–2346, 2007.

- [16] M.J. Gadlage, J.R. Ahlbin, B.L. Bhuva, N.C. Hooten, N.A. Dodds, R.A. Reed, L.W. Massengill, R.D. Schrimpf, and G. Vizkelethy, "Alpha-particle and focused-ion-beam-induced single-event transient measurements in a bulk 65-nm CMOS technology," IEEE Transactions on Nuclear Science, vol.58, no.3, pp.1093–1097, 2011.

- [17] R. Harada, Y. Mitsuyama, M. Hashimoto, and T. Onoye, "Impact of NBTI-induced pulse-width modulation on SET pulse-width measurement," IEEE Transactions on Nuclear Science, vol.60, no.4, pp.2630–2634, 2013.

- [18] N. Mikami, T. Nakauchi, A. Oyama, H. Kobayashi, and H. Usui, "Role of the deep parasitic bipolar device in mitigating the single event transient phenomenon," IEEE International Reliability Physics Symposium, pp.936–939, 2009.

- [19] C.L.M. de Boissac, F. Abouzeid, V. Malherbe, G. Gasiot, P. Roche, and J.L. Autran, "Influence of supply voltage and body biasing on single-event upsets and single-event transients in UTBB FD-SOI," IEEE Transactions on Nuclear Science, vol.68, no.5, pp.850–856, 2021.

- [20] R. Harada, Y. Mitsuyama, M. Hashimoto, and T. Onoye, "Set pulse-width measurement eliminating pulse-width modulation and within-die process variation effects," IEEE International Reliability Physics Symposium, pp.SE.1.1–SE.1.6, 2012.

- [21] Z. Li, L. Berti, J. Wouters, J. Wang, and P. Leroux, "Characterization of the total charge and time duration for single-event transient voltage pulses in a 65-nm cmos technology," IEEE Transactions on Nuclear Science, vol.69, no.7, pp.1593–1601, 2022.

- [22] D. Kung and R. Puri, "Optimal P/N width ratio selection for standard cell libraries," 1999 IEEE/ACM International Conference on Computer-Aided Design. Digest of Technical Papers (Cat. No.99CH37051), pp.178–184, 1999.

- [23] L.W. Massengill, O.A. Amusan, S. Dasgupta, A.L. Sternberg, J.D. Black, A.F. Witulski, B.L. Bhuva, and M. Alles, "Soft-error charge-sharing mechanisms at sub-100nm technology nodes," 2007 IEEE International Conference on Integrated Circuit Design and Technology, pp.1–4, 2007.

- [24] J. Chen, J. Yu, P. Yu, B. Liang, and Y. Chi, "Characterization of the effect of pulse quenching on single-event transients in 65-nm twin-well and triple-well cmos technologies," IEEE Transactions on Device and Materials Reliability, vol.18, no.1, pp.12–17, 2018.

- [25] J.S. Kauppila, T.D. Loveless, R.C. Quinn, J.A. Maharrey, M.L. Alles, M.W. McCurdy, R.A. Reed, B.L. Bhuva, L.W. Massengill, and K. Lilja, "Utilizing device stacking for area efficient hardened soi flip-flop designs," 2014 IEEE International Reliability Physics Symposium, pp.SE.4.1–SE.4.7, 2014.

- [26] J. Standard, "Measurement and reporting of alpha particle and terrestrial cosmic ray-induced soft errors in semiconductor devices," JESD89B, September, 2021.

- [27] Y.M. Aneesh and B. Bindu, "A physics-based single event transient pulse width model for CMOS VLSI circuits," IEEE Transactions on Device and Materials Reliability, vol.20, no.4, pp.723–730, 2020.

- [28] D.A. Black, W.H. Robinson, I.Z. Wilcox, D.B. Limbrick, and J.D. Black, "Modeling of single event transients with dual doubleexponential current sources: Implications for logic cell characterization," IEEE Transactions on Nuclear Science, vol.62, no.4, pp.1540– 1549, 2015.

- [29] J.R. Ahlbin, L.W. Massengill, B.L. Bhuva, B. Narasimham, M.J. Gadlage, and P.H. Eaton, "Single-event transient pulse quenching in advanced CMOS logic circuits," IEEE Transactions on Nuclear Science, vol.56, no.6, pp.3050–3056, 2009.

- [30] K. Zhang, R. Yamamoto, J. Furuta, K. Kobayashi, and H. Onodera, "Parasitic bipolar effects on soft errors to prevent simultaneous flips of redundant flip-flops," 2012 IEEE International Reliability Physics Symposium (IRPS), pp.5B.2.1–5B.2.4, 2012.

- [31] J.R. Ahlbin and P. Gadfort, "Impact of ultra-low voltages on singleevent transients and pulse quenching," 2014 SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), pp.1–3, 2014.

**Jun Furuta** was born in Gifu, Japan, in 1986. He received the B.E., M.E., and Ph.D. degrees in electrical and electronic engineering in informatics from Kyoto University, Kyoto, Japan, in 2009, 2011, and 2014, respectively. In 2014, he joined the Kyoto Institute of Technology as a specially appointed Assistant Professor, where he was then promoted to an Assistant Professor in 2017.

Shotaro Sugitani was born in Kyoto, Japan in 1998. He received the B.E. degree in Electronics and System Engineering from Kyoto Institute of Technology, Kyoto, Japan in 2022. He is currently a master course student at Kyoto Institute of Technology. He is a student member of IEEE, IPSJ and IEICE.

Ryuichi Nakajima was born in Hiroshima, Japan in 1997. He received the B.E. and the M.E. degree in Electronics and System Engineering from Kyoto Institute of Technology, Kyoto, Japan in 2021 and 2023, respectively. He is currently a doctoral course student at Kyoto Institute of Technology. He is a student member of IEEE, IPSJ and IEICE.

**Takafumi Ito** was born in Shiga, Japan in 1998. He received the B.E. and the M.E. degree in Electronics and System Engineering from Kyoto Institute of Technology, Kyoto, Japan in 2021 and 2023, respectively. He is a member of IPSJ.

**Kazutoshi Kobayashi** received his B.E., M.E., and Ph. D. in Electronic Engineering from Kyoto University, Japan in 1991, 1993, 1999, respectively. Starting as an Assistant Professor in 1993, he was promoted to an Associate Professor in the Graduate School of Informatics, Kyoto University in 2001, and stayed in that position until 2009. For two years during this time, he acted as an Associate Professor of VLSI Design and Education Center (VDEC) at the University of Tokyo. Since 2009, he has been a Professor

at Kyoto Institute of Technology. While in the past he focused on reconfigurable architectures utilizing device variations, his current research interest is in improving the reliability (Soft Errors, Bias Temperature Instability and Plasma Induced Damage) of current and future VLSIs. He started a research project related to gate drivers for GaN and SiC transistors since 2013. In 2022, he was nominated for one of the project managers of Moonshot Goal 6 "Realization of a fault-tolerant universal quantum computer that will

revolutionize economy, industry, and security by 2050" and organized his project team named "Development of Scalable Highly Integrated Quantum Bit Error Correction System" abbreviated as QUBECS. He was the recipient of the IEICE best paper award in 2009, the IRPS best poster award in 2013, the ICICDT best paper award in 2019 and the IEICE Electronics Society award in 2021.