# **Reduced Peripheral Leakage Current in Pin Photodetectors of Ge** on n<sup>+</sup>-Si by P<sup>+</sup> Implantation to Compensate Surface Holes

Koji ABE<sup>†</sup>, Mikiya KUZUTANI<sup>†</sup>, Satoki FURUYA<sup>†</sup>, Jose A. PIEDRA-LORENZANA<sup>†</sup>, Takeshi HIZAWA<sup>†</sup>, Nonmembers, and Yasuhiko ISHIKAWA<sup>†a)</sup>, Member

**SUMMARY** A reduced dark leakage current, without degrading the near-infrared responsivity, is reported for a vertical pin structure of Ge photodiodes (PDs) on n<sup>+</sup>-Si substrate, which usually shows a leakage current higher than PDs on p<sup>+</sup>-Si. The peripheral/surface leakage, the dominant leakage in PDs on n<sup>+</sup>-Si, is significantly suppressed by globally implanting P<sup>+</sup> in the i-Si cap layer protecting the fragile surface of i-Ge epitaxial layer before locally implanting B<sup>+</sup>/BF<sub>2</sub><sup>+</sup> for the top p<sup>+</sup> region of the pin junction. The P<sup>+</sup> implantation compensates free holes unintentionally induced due to the Fermi level pinning at the surface/interface of Ge. By preventing the hole conduction from the periphery to the top p<sup>+</sup> region under a negative/reverse bias, a reduction in the leakage current of PDs on n<sup>+</sup>-Si is realized.

key words: Ge epitaxial layer, near-infrared photodetector, Si photonics, peripheral leakage current

# 1. Introduction

A near-infrared (NIR) photodiode (PD) using a Ge epitaxial layer on Si (or Si-on-insulator, SOI) is one of the fundamental building blocks in Si photonics [1]. Ge exhibits a substantial optical absorption coefficient  $(>1000 \text{ cm}^{-1})$  at the NIR optical communication wavelengths (1.3–1.6 µm) as well as the good compatibility with the Si CMOS process. A vertical pin structure of Ge PD has been integrated with a Si optical waveguide on an SOI wafer for the on-chip optical communication [2]–[7], although a lateral pin structure has recently attracted interests regarding ultrahigh frequency response over 50 GHz [8], [9] to enhance the communication capacity. The vertical pin structure also plays a significant role in free-space/normal-incidence PD arrays required in applications such as multicore-fiber communications [10] and NIR sensing including the eye-safe light detection and ranging (LiDAR) [11]. In vertical pin PDs, an n<sup>+</sup>-Ge/i-Ge/p<sup>+</sup>-Si structure (PD on p<sup>+</sup>-Si) has been commonly used because of the dark leakage current lower than that in an inversely ordered structure of p<sup>+</sup>-Ge/i-Ge/n<sup>+</sup>-Si (PD on n<sup>+</sup>-Si) [12], [13]. However, the inverted configuration of PD on  $n^+$ -Si is convenient for the connection to the next stage circuit such as a transimpedance amplifier, which is usually designed to receive a positive photocurrent from the p contact. As previously reported by the authors [14], the higher leakage current in the PDs on n<sup>+</sup>-Si is ascribed to the peripheral/surface leakage, rather than the leakage due to the thermal generation of carriers via gap defects of threading dislocations in the i-Ge layer on Si, which is dominant in the PDs on  $p^+$ -Si [15]. The peripheral leakage in the PDs on n<sup>+</sup>-Si is probably derived from free holes [14] unintentionally induced due to the Fermi level pinning at the surface/interface of Ge [16], [17]. These holes induce an electrical conduction from the periphery to the top p<sup>+</sup> region of the PD on n<sup>+</sup>-Si under a negative/reverse bias, whereas such a conduction is suppressed in the case of the PDs on p<sup>+</sup>-Si because of the top n<sup>+</sup> region electrically isolated from the peripheral holes via a pn junction. One way to suppress the peripheral leakage in the PDs on n<sup>+</sup>-Si is to use a mesa structure [14], while the footprint of the photodetection area is reduced because inclined {113} facet sidewalls surround a Ge mesa on (001) Si by a selective growth [1].

In this work, a reduction in the leakage current of nonmesa/planar Ge PDs on n<sup>+</sup>-Si is realized by a P<sup>+</sup> implantation globally in the i-Si cap layer on the i-Ge epitaxial layer before locally forming the top p<sup>+</sup> region of the pin junction. The peripheral holes are compensated, leading to a reduced leakage current comparable to PDs on p<sup>+</sup>-Si.

# 2. Holes Induced at Ge Surface/Interface

To verify the presence of free holes at the Ge surface/interface, the Hall effect measurements were performed for Ge epitaxial layers grown by ultrahigh-vacuum chemical vapor deposition (UHV-CVD) with 9%-GeH<sub>4</sub>/Ar as a source gas. Here, an undoped Ge layer of 500 nm in thickness was prepared on a 6-inch bonded SOI wafer having a 250-nm-thick top (001) p-Si layer (approximately  $10 \Omega$  cm) and a 3-µm-thick buried SiO<sub>2</sub> layer. As in previous studies [13]–[15], a low/high temperature two-step growth was carried out to obtain a Ge layer uniform in thickness, i.e., a buffer layer (~50 nm) of elemental Ge was grown at a low temperature of 370°C, followed by a growth at an elevated temperature of 600°C. After the growth, the wafer was cut into pieces, and several different thicknesses of Ge were prepared by a wet etching in a H<sub>2</sub>O<sub>2</sub> solution. All samples showed the p-type conduction, independent of the thickness, and the sheet resistances were as low as  $20 \text{ k}\Omega/\text{sq.}$ , which is approximately one order of magnitude lower than 400 k $\Omega$ /sq. for the top Si layer of the SOI substrate. Thus, the observed p-type conduction is ascribed to holes in Ge.

Manuscript received August 29, 2023.

Manuscript revised February 7, 2024.

Manuscript publicized May 15, 2024.

<sup>&</sup>lt;sup>†</sup>Department of Electrical and Electronic Information Engineering, Toyohashi University of Technology, Toyohashi-shi, 441– 8580 Japan.

a) E-mail: ishikawa@ee.tut.ac.jp

DOI: 10.1587/transele.2023FUS0001

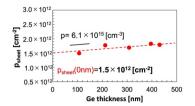

**Fig.1** Sheet hole densities of the Ge epitaxial layer as a function of the Ge thickness.

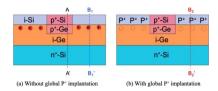

**Fig.2** Schematic cross-sections of PDs. (a) PD without the global  $P^+$  implantation and (b) PD with the global  $P^+$  implantation to compensate the free holes at the Ge surface.

Figure 1 shows the sheet hole density as a function of the Ge thickness. The hole density slightly decreased with decreasing the Ge thickness. The slope, or the hole density per unit volume in the undoped Ge layer was estimated as low as  $6 \times 10^{15}$  cm<sup>-3</sup>. More importantly, there is an offset in the sheet hole density at the Ge thickness of 0 nm, which is approximately  $1.5 \times 10^{12}$  cm<sup>-2</sup>. This indicates the presence of free holes at the top Ge surface and/or bottom Ge/Si interface, although the densities cannot be divided between the top surface and bottom interface.

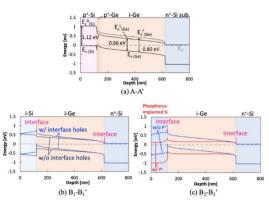

The peripheral leakage in the PDs on n<sup>+</sup>-Si is attributed to the holes at the top Ge surface [14], as shown in Fig. 2 (a). These holes easily induce a leakage current from the periphery to the top  $p^+$  region of the PD under a negative/reverse bias. Typical calculated energy band diagrams along the lines A-A' and  $B_1$ - $B_1$ ' of Fig. 2 (a) are shown in Figs. 3 (a) and 3 (b), respectively. Here, the bandgap narrowing of a few 10 meV in Ge was ignored, which is induced by the tensile in-plane lattice strain of about 0.2% in Ge due to the thermal expansion mismatch with the Si substrate [1], [14], [15]. Similar to the main part of p<sup>+</sup>-Si/p<sup>+</sup>-Ge/i-Ge/n<sup>+</sup>-Si PD in Fig. 3 (a), the diagram at the periphery in Fig. 3 (b) shows that the Fermi level is located near the valence band maximum of Ge at the top i-Si/i-Ge interface in the presence of the interface holes with the sheet density of  $2.0 \times 10^{12}$  cm<sup>-2</sup>. It is mentioned that the holes at the bottom interface are compensated with electrons in the n<sup>+</sup>-Si substrate, i.e., there is no significant difference in the band diagram at around the bottom interface between the presence and absence of the interface holes, as shown in Fig. 3 (b).

To suppress the peripheral leakage by the free holes at the top i-Si/i-Ge interface, an implantation of P<sup>+</sup> in a Si cap layer on Ge should be effective to compensate the holes, as shown in Fig. 2 (b). The band diagram along the line  $B_2$ - $B_2$ ' of Fig. 2 (b) is shown in Fig. 3 (c). Here, a uniform P<sup>+</sup> density of  $2.0 \times 10^{17}$  cm<sup>-3</sup> was assumed in the top n-Si layer of 120 nm in thickness. This corresponds to the

**Fig. 3** Calculated energy band diagrams for (a) the main part of p<sup>+</sup>-Si (120 nm)/p<sup>+</sup>-Ge (20 nm)/i-Ge (480 nm)/n<sup>+</sup>-Si PD (along the line A-A' in Fig. 2 (a)), (b) the i-Si/i-Ge/n<sup>+</sup>-Si structure comparing the presence and absence of the holes at the top and bottom interfaces with the sheet density of  $2 \times 10^{12}$  cm<sup>-2</sup> (along the line B<sub>1</sub>-B<sub>1</sub>' in Fig. 2 (a)), and (c) the n-Si (P<sup>+</sup> implanted)/i-Ge/n<sup>+</sup>-Si structure (along the line B<sub>2</sub>-B<sub>2</sub>' in Fig. 2 (b)) compared with the i-Si/i-Ge/n<sup>+</sup>-Si structure. A uniform P<sup>+</sup> density of  $2.0 \times 10^{17}$  cm<sup>-3</sup> in the top Si layer was assumed in (c).

sheet P<sup>+</sup> density of  $2.4 \times 10^{12}$  cm<sup>-2</sup>, almost equal to the interface hole density of  $2.0 \times 10^{12}$  cm<sup>-2</sup>. In contrast to the absence of the P<sup>+</sup> implantation, the Fermi level is not located near the valence band maximum of Ge but located near the midgap. This indicates the compensation of the interface holes, potentially preventing the peripheral leakage.

### 3. PD Preparation

Ge PDs on n<sup>+</sup>-Si were prepared as follows. As the starting substrate, an Sb-doped n<sup>+</sup>-Si (001) wafer was used, whose resistivity was  $0.008-0.020 \Omega$  cm. First, an undoped Ge epitaxial layer of 500 nm in thickness was grown on n<sup>+</sup>-Si by UHV-CVD. The growth condition was exactly the same as that for the Hall effect measurements in the previous section. Subsequently, a Si cap layer of 120 nm in thickness was grown at 600°C for protecting the fragile surface of Ge using a source gas of 10%-Si<sub>2</sub>H<sub>6</sub>/Ar. A post-growth annealing was performed at 800°C for 10 min in N<sub>2</sub> to reduce the threading dislocation density in Ge [15].

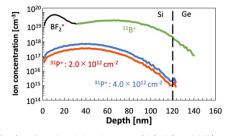

To compensate holes at the Ge surface (Si cap/Ge interface), a P<sup>+</sup> implantation was performed in the Si cap layer over the entire surface, or globally. Based on the Hall effect measurements, a dose of  $2.0 \times 10^{12}$  cm<sup>-2</sup> was used, although a different dose of  $4.0 \times 10^{12} \text{ cm}^{-2}$  was also used for comparison. The acceleration voltage was 35 kV, leading to the P<sup>+</sup> distribution mostly in the Si cap layer, as simulated in Fig. 4. Then, to form a vertical pin junction, an implantation of  $B^+$  and  $BF_2^+$  was performed locally with resist masks. The  $B^+$  and  $BF_2^+$  were implanted at 10 kV with doses of  $2.0 \times 10^{14}$  cm<sup>-2</sup> and  $1.0 \times 10^{14}$  cm<sup>-2</sup>, respectively. As shown in Fig. 4, because of the difference in the penetration depth, the B<sup>+</sup> ions were implanted across the Si cap/Ge interface to form the p region in the Ge layer, while the  $BF_2^+$  ions were distributed near the surface of the Si cap layer, realizing a low resistance with a metal contact. The implanted area, cor-

Fig. 4 Simulated distributions of P<sup>+</sup>, B<sup>+</sup> and BF<sub>2</sub><sup>+</sup> ions.

responding to the junction/PD area, was square-shaped with different widths W of 20–500  $\mu$ m. An activation annealing was performed at 600°C for 5 min in N<sub>2</sub>. Finally, metal electrodes of Al/Ti (with an illumination window opening) were formed. In addition to the PDs on n<sup>+</sup>-Si, Ge PDs on p<sup>+</sup>-Si were prepared as references.

Current-voltage (I-V) characteristics were measured at room temperature (RT) under dark to investigate the leakage current. I-V curves under a light illumination of 1.23 mW at 1550 nm were also measured. Furthermore, responsivity spectra were obtained at 1455–1640 nm.

#### 4. Results and Discussion

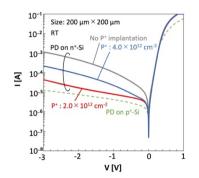

Figure 5 shows typical I-V characteristics at RT for PDs on  $n^+$ -Si with and without the P<sup>+</sup> implantation together with a reference PD on p<sup>+</sup>-Si. The width of the squared-shaped PD was 200 µm. Rectifying diode properties were obtained, although the reverse leakage current was different between the PDs. It is important that the P<sup>+</sup> implantation in the Si cap layer of the PDs on  $n^+$ -Si successfully reduced the dark leakage current. The lower dose of  $2.0 \times 10^{12}$  cm<sup>-2</sup> more efficiently reduced the leakage current, which was comparable to that in the PD on p<sup>+</sup>-Si.

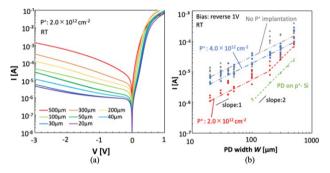

To examine the leakage mechanism, I-V characteristics for different PD widths were obtained. A typical width dependence is shown in Fig. 6 (a) for the PDs on n<sup>+</sup>-Si with the P<sup>+</sup> implantation dose of  $2.0 \times 10^{12}$  cm<sup>-2</sup>. The reverse leakage decreased with decreasing the PD width. In Fig. 6 (b), the leakage current at the reverse voltage of 1 V was plotted as a function of the width W. The leakage current I should be composed of peripheral and areal components, and is expressed in the case of the square-shaped PD as

$$I = J_{periphery} 4W + J_{area} W^2, \tag{1}$$

where  $J_{periphery}$  and  $J_{area}$  correspond to the peripheral leakage current per unit length and the one per unit area, respectively. In the logarithmic plot of Fig. 6 (b), the slope of 2 corresponds to the leakage current dominated by the area of the pin junction, whereas the slope of 1 corresponds to the leakage current dominated by the peripheral length. For the reference PDs on p<sup>+</sup>-Si, the slope was almost equal to 2, indicating that the leakage current is dominated by the areal leakage. As in the previous report [15], the areal leakage is derived from the thermal generation of carriers via gap defects of threading dislocations in the i-Ge layer.

Fig. 5 Typical I-V characteristics of the fabricated Ge PDs.

**Fig.6** (a) Typical I-V characteristics of the Ge PDs on n<sup>+</sup>-Si (the P<sup>+</sup> implantation dose of  $2.0 \times 10^{12}$  cm<sup>-2</sup>) with different PD widths, and (b) the leakage current at the reverse voltage of 1 V as a function of the PD width.

Table 1

A comparison of leakage current of the PDs at 1-V reverse bias.

| Sample                   |                                                 | J <sub>periphery</sub><br>[mA/cm] | J <sub>area</sub><br>[mA/cm <sup>2</sup> ] |

|--------------------------|-------------------------------------------------|-----------------------------------|--------------------------------------------|

| PD on p <sup>+</sup> -Si |                                                 | N.A.                              | 9.3                                        |

| PD on n <sup>+</sup> -Si | No P <sup>+</sup> implantation                  | 3.4                               | N.A.                                       |

|                          | $P^+: 2.0 \times 10^{12} \text{ cm}^{-2}$       | 0.6                               | 30.0                                       |

|                          | $P^+$ : 4.0 × 10 <sup>12</sup> cm <sup>-2</sup> | 2.0                               | N.A.                                       |

In contrast, the PDs on n<sup>+</sup>-Si without the P<sup>+</sup> implantation as well as those with the P<sup>+</sup> implantation dose of  $4.0 \times$  $10^{12} \text{ cm}^{-2}$  showed the slope of approximately 1, indicating a high peripheral leakage. However, the P<sup>+</sup> implantation with the dose of  $2.0 \times 10^{12}$  cm<sup>-2</sup> showed the slope of 2 for the width as large as 200 µm or larger, despite the slope of 1 for the smaller ones. This is a clear evidence of the reduction in the peripheral leakage by the appropriate P<sup>+</sup> implantation. As summarized in Table 1, Jperiphery was significantly reduced from 3.4 mA/cm (without the P<sup>+</sup> implantation) to 0.6 mA/cm by implanting P<sup>+</sup> with the dose of  $2.0 \times 10^{12}$  cm<sup>-2</sup>. However, no significant reduction in the leakage current was observed for the higher dose of  $4.0 \times 10^{12} \text{ cm}^{-2}$ . This is ascribed to the formation of electron channels because of an overdose to compensate the holes. The implantation dose and/or depth should be optimized for further reducing the leakage current.

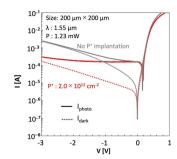

To examine the effect of the global  $P^+$  implantation on the photodetection efficiency, I-V curves were obtained under an NIR light illumination, as shown in Fig. 7. Independent of the  $P^+$  implantation, the light illumination at the wavelength of 1550 nm increased the reverse current due to the photocurrent, although at higher reverse voltage (V <

Fig. 7 Typical I-V characteristics of the 200- $\mu$ m-wide Ge PDs on n<sup>+</sup>-Si with and without an NIR light illumination (1.23 mW at 1550 nm).

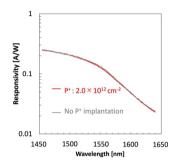

Fig. 8 Typical responsivity spectra at the reverse voltage of 1 V.

-2 V), the current increase was smeared for the PD without the P<sup>+</sup> implantation due to a rapid increase in the leakage current. The responsivity at 1550 nm was estimated to be 0.13 A/W, which is reasonable for the Ge absorption layer as thin as 500 nm. Furthermore, the responsivity spectra at 1455–1640 nm in Fig. 8 were identical between the PDs with and without the P<sup>+</sup> implantation. Therefore, no degradation in the spectral responsivity occurs by the global P<sup>+</sup> implantation, while reducing the dark leakage current in the Ge PDs on n<sup>+</sup>-Si.

## 5. Conclusion

A reduced dark leakage current, without degrading the NIR responsivity, was realized for a vertical pin structure of the Ge PDs on n<sup>+</sup>-Si substrate. In particular, the peripheral/surface leakage was significantly suppressed by globally implanting P<sup>+</sup> in the i-Si cap layer protecting the fragile surface of i-Ge epitaxial layer before locally implanting B<sup>+</sup>/BF<sub>2</sub><sup>+</sup> for the top p<sup>+</sup> region. The P<sup>+</sup> implantation compensates holes at the top Ge surface, preventing the hole conduction from the periphery to the top p<sup>+</sup> region under a negative/reverse bias.

## Acknowledgements

This work was partly supported by JSPS KAKENHI Grant Numbers JP21H01367 and JP22H01555.

#### References

J. Michel, J. Liu, and L.C. Kimerling, "High-performance Ge-on-Si photodetectors," Nat. Photon., vol.4, no.8, pp.527–534, Aug. 2010.

- [2] D. Ahn, C.-Y. Hong, J. Liu, W. Giziewicz, M. Beals, L.C. Kimerling, and J. Michel, "High performance, waveguide integrated Ge photodetectors," Opt. Express, vol.15, no.7, pp.3916–3921, April 2007.

- [3] T. Yin, R. Cohen, M.M. Morse, G. Sarid, Y. Chetrit, D. Rubin, and M.J. Paniccia, "31 GHz Ge n-i-p waveguide photodetectors on silicon-on-insulator substrate," Opt. Express, vol.15, no.21, pp.13965–13971, Oct. 2007.

- [4] L. Vivien, J. Osmond, J.-M. Fédéli, D. Marris-Morini, P. Crozat, J.-F. Damlencourt, E. Cassan, Y. Lecunff, and S. Laval, "42 GHz pin Germanium photodetector integrated in a silicon-on-insulator waveguide," Opt. Express, vol.17, no.8, pp.6252–6257, April 2009.

- [5] K.-W. Ang, T.-Y. Liow, M.-B. Yu, Q. Fang, J. Song, G.-Q. Lo, and D.-L. Kwong, "Low thermal budget monolithic integration of evanescent-coupled Ge-on-SOI photodetector on Si CMOS platform," IEEE J. Select. Topics Quantum Electron., vol.16, no.1, pp.106–113, Jan./Feb. 2010.

- [6] S. Park, T. Tsuchizawa, T. Watanabe, H. Shinojima, H. Nishi, K. Yamada, Y. Ishikawa, K. Wada, and S. Itabashi, "Monolithic integration and synchronous operation of germanium photodetectors and silicon variable optical attenuators," Opt. Express, vol.18, no.8, pp.8412–8421, April 2010.

- [7] H. Nishi, T. Tsuchizawa, R. Kou, H. Shinojima, T. Yamada, H. Kimura, Y. Ishikawa, K. Wada, and K. Yamada, "Monolithic integration of a silica AWG and Ge photodiodes on Si photonic platform for one-chip WDM receiver," Opt. Express, vol.20, no.8, pp.9312–9321, April 2012.

- [8] J. Fujikata, M. Noguchi, K. Kawashita, R. Katamawari, S. Takahashi, M. Nishimura, H. Ono, D. Shimura, H. Takahashi, H. Yaegashi, T. Nakamura, and Y. Ishikawa, "High-speed Ge/Si electro-absorption optical modulator in C-band operation wavelengths," Opt. Express, vol.28, no.22, pp.33123–33134, Oct. 2020.

- [9] S. Lischke, A. Peczek, J.S. Morgan, K. Sun, D. Steckler, Y. Yamamoto, F. Korndörfer, C. Mai, S. Marschmeyer, M. Fraschke, A. Krüger, A. Beling, and L. Zimmermann, "Ultra-fast germanium photodiode with 3-dB bandwidth of 265 GHz," Nat. Photon., vol.15, no.12, pp.925–931, Dec. 2021.

- [10] T. Umezawa, T. Sakamoto, A. Kanno, N. Yamamoto, and T. Kawanishi, "High Speed 2-D Photodetector Array for Space and Mode-Division Multiplexing Fiber Communications," J. Lightwave Technol., vol.36, no.17, pp.3684–3692, Sept. 2018.

- [11] C.-L. Chen, S.-W. Chu, B.-J. Chen, Y.-F. Lyu, K.-C. Hsu, C.-F. Liang, S.-S. Su, M.-J. Yang, C.-Y. Chen, S.-L. Cheng, H.-D. Liu, C.-T. Lin, K.P. Petrov, H.-W. Chen, K.-C. Chu, P.-C. Wu, P.-T. Huang, N. Na, and S.-L. Chen, "An Up-to-1400 nm 500 MHz Demodulated Time-of-Flight Image Sensor on a Ge-on-Si Platform," 2020 IEEE Int. Conf. Solid-State Circuits (ISSCC), 5.3, Feb. 2020.

- [12] G. Masini, L. Colace, G. Assanto, H.-C. Luan, and L.C. Kimerling, "High-performance p-i-n Ge on Si photodetectors for the near infrared: from model to demonstration," IEEE Trans. Electron Devices, vol.48, no.6, pp.1092–1096, June 2001.

- [13] K. Ito, T. Hiraki, T. Tsuchizawa, and Y. Ishikawa, "Waveguideintegrated vertical pin photodiodes of Ge fabricated on p<sup>+</sup> and n<sup>+</sup> Si-on-insulator layers," Jpn. J. Appl. Phys., vol.56, no.4S, 04CH05, April 2017.

- [14] Y. Ishikawa, K. Ito, K. Noguchi, and T. Hiraki, "Near-infrared pin Photodetectors of Ge Epitaxial Layers for Si Photonics," IEICE Trans. Electron. C, vol.J101-C, pp.374–380, Oct. 2018.

- [15] Y. Ishikawa and S. Saito, "Ge-on-Si photonic devices for photonicelectronic integration on a Si platform," IEICE Electron Express, vol.11, no.24, 20142008, Oct. 2014.

- [16] J. Tersoff, "Schottky barrier heights and the continuum of Gap States," Phys. Rev. Lett., vol.52, no.6, pp.465–468, Feb. 1984.

- [17] H. Hasegawa and H. Ohno, "Unified disorder induced gap state model for insulator–semiconductor and metal–semiconductor interfaces," J. Vac. Sci. Technol. B, vol.4, no.4, pp.1130–1138, July 1986.