# INVITED PAPER Special Section on Electronic Displays Self-Aligned Four-Terminal Planar Metal Double-Gate Low-Temperature Polycrystalline-Silicon Thin-Film Transistors for System-on-Glass

Akito HARA<sup>†a)</sup>, Member, Shinya KAMO<sup>†</sup>, and Tadashi SATO<sup>††</sup>, Nonmembers

SUMMARY Self-aligned four-terminal (4T) planar metal double-gate (DG) polycrystalline-silicon (poly-Si) thin-film transistors (TFTs) were fabricated on a glass substrate at a low temperature (LT), which is below 550°C, to realize high performance and low power dissipation system-onglass (SoG). The top gate (TG) and bottom gate (BG) were formed from tungsten (W); the BG was embedded in the glass substrate and the TG was fabricated by a self-alignment process using the BG as a photomask. This structure is called embedded metal double-gate (E-MeDG) in this paper. The poly-Si channel with lateral large grains was fabricated using a continuous-wave laser lateral crystallization (CLC). The self-aligned 4T E-MeDG LT poly-Si TFT, with a gate length of  $5\,\mu m$  and TG and BG SiO<sub>2</sub> thicknesses of 50 and 100 nm, respectively, exhibited a subthreshold swing of 120 mV/dec and a threshold voltage (V<sub>th</sub>) of -0.5 V in the connecting DG mode; i.e. when TG is connected to BG. In the TG operation at various BG control voltage, a threshold voltage modulation factor ( $\gamma$  =  $\Delta V_{th}/\Delta V_{BG}$ ) of 0.47 at negative BG control voltage and 0.60 at positive BG control voltage are demonstrated, which values are nearly equal to theoretical prediction of 0.40 and 0.75. Trend of subthreshold swing (s.s.) of TG operation under different BG control voltage are also consistent with theoretical prediction. In addition to TG operation, successful BG operation under various TG control voltages was confirmed. Field-effect mobility derived from gm also varied depending on control gate voltage. The high controllability of device parameter of individual LT poly-Si TFTs is caused by excellent crystalline quality of CLC poly-Si film and will enable us to the fabrication of high-speed and low power-dissipation SoG.

key words: poly-Si, TFT, double-gate, four-terminal, system-on-glass

# 1. Introduction

Low-temperature (LT) polycrystalline-silicon (poly-Si) thin-film transistors (TFTs) with a high on-current are attractive as pixel TFTs in high resolution mobile display such as active-matrix organic light-emitting diodes (AMOLED) and active-matrix liquid crystal displays (AMLCD). Particularly for system-on-glass (SoG), which is expected to be one candidate as future information mobile display, highperformance poly-Si TFTs must be fabricated on a transparent glass substrate in addition to high resolution display, so as to integrate logic and memory circuits monolithically. However, it is difficult for LT poly-Si TFTs on a glass substrate to scale down to the nanometer level because of, first, variation in the size of the glass substrate after the heating

a) E-mail: akito@mail.tohoku-gakuin.ac.jp

DOI: 10.1587/transele.E97.C.1048

process and, second, the surface roughness of the glass substrate. Thus, approaches that do not depend only on scaling are required to improve the performance of LT poly-Si TFTs on glass substrate.

Multigate structures such as double, triple, pi, omega, and gate-all-around structures can potentially be used to realize ideal Si transistors in a nanometer-scale complementally metal-oxide-semiconductor (CMOS) era. Such multigate structures have attracted considerable attention in the area of poly-Si TFTs [1]–[51], for three dimensional (3D) large-scale integrated (LSI) circuits in addition to display application. One of the authors of this paper (A. H.) previously reported self-aligned planar metal double-gate lowtemperature (LT) poly-Si TFTs in which a tungsten (W) bottom gate (BG) was embedded in a glass substrate, a W top gate (TG) was fabricated by a self-alignment process using the BG as a photomask, and the TG and BG were electrically connected each other. These TFTs are called embedded metal double-gate LT poly-Si TFTs (E-MeDG LT poly-Si TFTs) [50], [51]. The E-MeDG LT poly-Si TFTs comprise lateral grains larger than  $2\mu m$ , which are fabricated using diode-pumped solid-state (DPSS) continuous-wave (CW) laser lateral crystallization, which is called the CLC method [52], [53]. The E-MeDG LT poly-Si TFTs exhibited high performance with a nominal mobility greater than  $500 \text{ cm}^2/\text{Vs}$  and a subthreshold swing (s.s.) of 140 mV/dec. However, it was difficult to control threshold voltage  $(V_{th})$ because a thin undoped poly-Si film (75-nm-thick) was used, and the same metal gate material was used for both n-ch and p-ch TFTs. For fabricating high performance and low-power-dissipation circuits on a glass substrate for SoG, it is necessary to control V<sub>th</sub> of TFTs. As mentioned earlier, we have already developed the fabrication process for self-aligned E-MeDG LT poly-Si TFTs. In this work, we fabricated four-terminal (4T) self-aligned E-MeDG poly-Si TFTs by modulating the self-aligned E-MeDG LT poly-Si TFT fabrication procedure. The high V<sub>th</sub> controllability, their small s.s, and high mobility of self-aligned 4T E-MeDG LT poly-Si TFTs will enable us to fabricate highspeed and low-power-dissipation CMOS circuits on a glass substrate.

# 2. Device Fabrication

Fused quartz glass was used as the substrate in this exper-

Manuscript received February 26, 2014.

<sup>&</sup>lt;sup>†</sup>The authors are with Tohoku Gakuin University, Chuo-1, Tagajo, 985-8537 Japan.

<sup>&</sup>lt;sup>††</sup>The author is with Hiroshima University, 1-4-2 Kagamiyama, Higashi-Hiroshima, 739-8527 Japan.

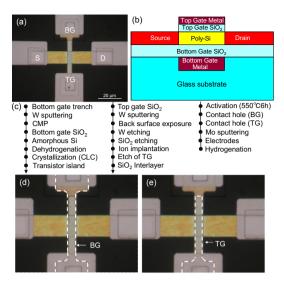

**Fig. 1** (a) Top-view image of a completed 4T E-MeDG LT poly-Si TFT, (b) gate stack of 4T E-MeDG LT poly-Si TFT, (c) process flow of 4T E-MeDG LT poly-Si TFT, (d) layout of BG, and (e) layout of TG.

iment. Figure 1(a) and (b) show a top-view photograph of the completed TFT and schematic diagram of cross-section of the 4T E-MeDG LT poly-Si TFTs, respectively. Figure 1(c) shows the process steps involved in the fabrication procedure.

After the fabrication of the BG trench into the glass substrate using reactive ion etching (RIE), a tungsten (W) film was deposited by sputtering at 325°C. The W gate was selected because the work function of W is nearly in the middle of the Si band gap. In addition, W is a refractory metal, and W chemical mechanical polishing (CMP) slurry is commercially available. Next, CMP was employed to form an embedded BG. A 100 nm-thick BG SiO<sub>2</sub> layer and a 75 nm-thick undoped amorphous Si (a-Si) layer were then deposited using PECVD at 325°C. After dehydrogenation annealing in N<sub>2</sub> gas at 500°C for 60 min, the a-Si layer was transformed into a poly-Si film using the CLC method. Overlap laser scanning along the source-drain (SD) direction was used to coat the substrate with a uniform lateralgrained poly-Si film. After the formation of transistor islands, a 50 nm-thick TG SiO<sub>2</sub> layer was deposited using PECVD at 325°C and, then, sputtering of W with a thickness of 40 nm and, next, a positive resist was coated. We used the self-alignment process to fabricate the TG by carrying out back-surface exposure of the g-line using the embedded BG as a photomask. This technique is advantageous for glass substrates. In generally, heat process changes glass size, but this technique enable us to apply self-alignment process even after heat treatment processes. The top W layer was removed by RIE using  $CF_4+O_2$  to form top W gate metal. Subsequently, the SiO<sub>2</sub> layer on the S/D region was removed by dry etching using the TG as a self-aligned mask. The SD regions were doped with phosphorous by ion implantation; the acceleration energy and ion dose used were 10 KeV and  $2 \times 10^{15}$  cm<sup>-2</sup>, respectively. After the removal of the TG edge region in order to open the space to

connect the electrode and the BG, an SiO<sub>2</sub> isolation layer was formed through PECVD at  $325^{\circ}$ C, following which activation annealing was performed at  $550^{\circ}$ C for 6 h in N<sub>2</sub>. After the formation of a contact hole to connect the electrode and BG, a contact hole connecting the electrode and TG and S/D was formed. Further, an Mo electrode was deposited by sputtering. Finally, hydrogenation was performed through step cooling [54]. Figure 1(d) and (e) show the layouts of the BG and TG, respectively. The device fabrication was performed at a maximum temperature of 550°C.

## 3. Experimental Results

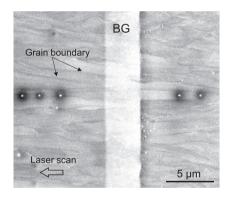

Figure 2 shows field-emission scanning electron microscopy (FE-SEM) photograph of CLC poly-Si film on BG. Vertical white ribbon in central region corresponds to BG and several white dots correspond to markers to achieve other evaluations of poly-Si film. The poly-Si film was treated by Secco's solution to clarify grain boundaries. It is confirmed that lateral growth of poly-Si was performed without breaking its lateral growth on BG and, as a result, lateral large grains with length more than 5  $\mu$ m are formed.

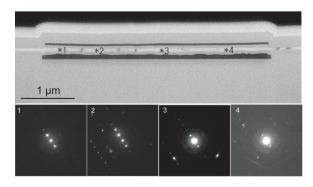

Cross sectional transmission electron microscopy (TEM) of TFTs with bottom gate  $SiO_2$  thickness being 50 nm-thick is shown in Fig. 3. The surface of BG includes strong roughness caused by CMP. This figure in-

**Fig.2** Field-emission scanning electron microscopy (FE-SEM) image of lateral large grains on BG. To observe grain boundaries, Secco's etching was performed.

**Fig. 3** Cross-sectional transmission electron microscopy of 4T E-MeDG LT poly-Si TFT and electron diffraction pattern at four different points in channel region.

cludes electron diffraction pattern at four points in channel region. Though intensity of diffraction spots is different at every measuring points, they show resemble pattern.

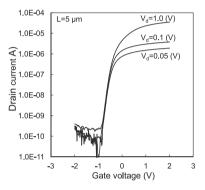

Figure 4 shows the transfer characteristics of the 4T E-MeDG LT poly-Si TFT with gate length of  $5\,\mu\text{m}$  in the connecting DG mode under drain voltage of 50, 100 mV and 1.0 V; i.e. when TG is connected to BG. A steep on-current increase with subthreshold swing (s.s.) of 120 mV/dec and V<sub>th</sub> of -0.5 V was observed.

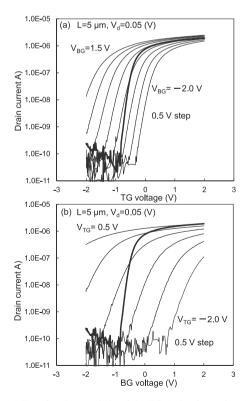

Figure 5 (a) shows the transfer characteristics of the TG operation of the 4T E-MeDG LT poly-Si TFTs for different BG control voltages ( $V_{BG}$ ). In this case, drive gate and control gate correspond to TG and BG, respectively. The TG

**Fig. 4** Transfer characteristics of the 4T E-MeDG LT poly-Si TFT in the connecting DG mode with drain voltages of 50, 100, and 1000 mV.

**Fig.5** (a) Transfer characteristic of the TG derive for various BG voltages. (b) Transfer characteristic of the BG drive for various TG voltages. Bold solid lines in each figure show the transfer characteristic of the connecting double-gate mode shown in Fig. 4.

voltage was swept from -2.0 V to 2.0 V with drain voltage of 50 mV and BG control voltage was changed with 0.5 V steps from -2.0 to 1.5 V. Bold solid line in this figure shows transfer characteristic of connected DG mode under drain voltage of 50 mV. The V<sub>th</sub> was shift from negative to positive with decreasing BG control voltage. Figure 5 (b) shows the transfer characteristics of the BG operation of the 4T E-MeDG LT poly-Si TFTs under different TG control voltages (V<sub>TG</sub>). In this case, drive gate and control gate become BG and TG, respectively. The V<sub>th</sub> was shifted from negative to positive with decreasing control voltage, but the amount of shift of V<sub>th</sub> at each step is larger than that at TG operation.

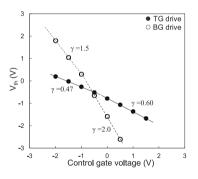

Figure 6 shows V<sub>th</sub> of drive TFT under different control gate voltage, in which V<sub>th</sub> was determined from linear extrapolation method under V<sub>d</sub>=0.05 V. We defined  $\gamma$  as modulation magnitude of V<sub>th</sub> of drive TFT under small variation of control gate voltage (V<sub>CG</sub>), namely  $\gamma = |\Delta V_{th}/\Delta V_{CG}|$ , according to research of M. Masahara et al. [55], [56], where  $\Delta V_{th}$  means variation of threshold voltage of drive TFT and  $\Delta V_{CG}$  means small variation of control gate voltage. In the case of TG operation under different BG control voltage,  $\gamma$ of 0.47 at negative BG control voltage and 0.60 at positive BG control voltage are obtained. While, in the BG operation under different TG control voltage, they show 1.5 and 2.0, respectively.

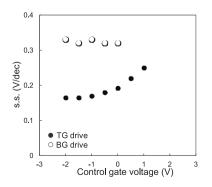

Figure 7 shows variation of s.s. of drive TFT under different control gate voltage. The s.s. of TG operation under negative BG control voltage becomes smaller than those of positive BG control voltage, while s.s. of BG operation under different TG control voltage is larger than those of TG operation.

**Fig. 6**  $\gamma$  as a function of various control gate voltages.

Fig. 7 The s.s. as a function of various control gate voltages.

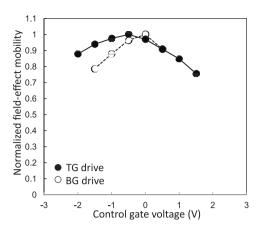

Fig. 8 Variation in field-effect mobility for various control gate voltages. The mobility was normalized by the maximum value.

Figure 8 shows filed-effect mobility of TG and BG operations, respectively. They are normalized by maximum mobility of each mode. The maximum field-effect mobility of TG and BG operation are both  $165 \text{ cm}^2/\text{Vs}$ , which are calculated from g<sub>m</sub>. The filed-effect mobility of each mode shows convex shape; namely, they decrease at positive and negative control gate voltage. Ratio of reduction of mobility is larger for BG operation than that of TG operation.

#### 4. Discussion

Our crystallization method facilitates the formation of large grains over a wide range of laser-beam energies at high laser-scanning speeds. Laser scanning generates a temperature gradient at the liquid-solid interface, in which front (molten Si) and rear (solid Si) regions are high and low, respectively, stabilizes the crystallization process and leads to formation of lateral large grain. This mechanism is expected to be established on BG, because the region of BG is localized to small area compared to the size of laser beam (400  $\times 20 \,\mu m^2$ ). Other mechanism to makes easy to form lateral large grains on BG is that there is no step at boundaries between glass and embedded BG due to application of CMP process. The flat surface suffers from nucleation of crystalline defects during solidification.

An excellent s.s. of 120 mV/dec was performed in the connecting DG mode because of operation as a fullydepleted mode. This mode is achieved by following mechanisms. The first is that poly-Si film is made up of high quality film with large grains. This leads to low electrical defects in channel region. Another mechanism is that the poly-Si film is undoped and thin. As a result of combination of these effects, the potential of the Si channel becomes nearly constant in depth in the subthreshold region. This phenomenon is known as "volume inversion," in which the potential of Si directly follows the gate voltage [57]. This leads to a steep increase in the drain current in the connecting DG mode in the subthreshold region.

Next, we discuss modulation factor of  $\gamma = |\Delta V_{th}/\Delta V_{CG}|$ . The  $\gamma$  in BG drive are very larger than those of TG drive.

**Table 1**Comparison of  $\gamma$  and s.s.

|                | TG drive(BG control) |      |             |      | BG drive(TG control) |     |             |      |

|----------------|----------------------|------|-------------|------|----------------------|-----|-------------|------|

|                | γ                    |      | s.s.(V/dec) |      | γ                    |     | s.s.(V/dec) |      |

| Control gate   | N                    | Р    | N           | Р    | N                    | Р   | N           | Р    |

| Theory         | 0.40                 | 0.75 | 0.08        | 0.11 | 1.3                  | 2.5 | 0.14        | 0.21 |

| Experiment     | 0.47                 | 0.60 | 0.16        | 0.25 | 1.5                  | 2.0 | 0.32        | -    |

| N:negative, P: | positive.            |      |             |      |                      | 1   |             |      |

This is reasonable because large gate voltage swing of BG is required for small variation of TG control voltage owing to thick BG SiO<sub>2</sub> and thin TG SiO<sub>2</sub> thickness. The s.s. value in TG drive under negative BG control voltage becomes small than those of TG drive with positive BG control voltage. This is caused by generation of back (bottom) channel when positive BG control voltage is applied. The s.s. values of BG drive is inferior to those of TG drive due to thick BG gate SiO<sub>2</sub> thickness.

To achieve more detail analysis of  $\gamma$  and s.s., we compared  $\gamma$  of our data with theoretical approach done by M. Masahara et al. [55], [56]. Their simple model is based on following assumption that, first, Si channel is thin and undoped single crystal, which is free from crystalline defects, and second, interface charge states between Si/SiO<sub>2</sub> and defects in  $SiO_2$  are absent. Though these assumptions are not necessary satisfied for LT poly-Si TFTs, we used their model for simple analysis of our data. According to their model,  $\gamma$  becomes 0.40 and 0.75 for TG drive at negative and positive BG control voltage, respectively. For BG drive under TG as a control gate,  $\gamma$  are 1.3 and 2.5 at negative and positive TG control voltage, respectively. The s.s. of TG drive under negative and positive BG control voltage are 0.08 and 0.11, respectively. While, s.s. of BG drive under negative and positive TG control voltage are 0.14 and 0.21, respectively. These data are summarized in Table 1 with experimental results. Trend in theoretical prediction is consistent with experimental data, but with slight different from experimental data. This is caused by, first, existence of electrical defects caused by grain boundaries of poly-Si film and, second, existence of interface state at SiO<sub>2</sub>/Si and defects charge state in SiO<sub>2</sub> due to fabrication of SiO<sub>2</sub> by PECVD, and, third, low temperature TFT fabrication process at 550°C.

Maximum field-effect mobility of TG and BG drive was  $165 \text{ cm}^2/\text{Vs}$ . This is relatively small compared to those of previously reported CLC LT poly-Si TFTs [50], [51]. This may be caused by insufficient optimization of S/D region in 4T E-MeDG LT poly-Si TFTs. As shown in Fig. 3, poly-Si film thickness of S/D region becomes thinner than 75 nm, which is caused by over etching at process to remove top gate  $SiO_2$  layer on S/D region. Thin S/D leads to high resistance of this region and, as a consequane, this leads to inferior field-effect mobility which calculated from g<sub>m</sub>. Reduction of mobility at negative control gate voltage is caused by increase of carrier scattering owing to ion- and roughness-scattering by pushing electron to TG SiO<sub>2</sub>/Si interface for TG drive [58]. Same mechanism leads to reduction of mobility of BG drive because of electron pushing to BG SiO<sub>2</sub>/Si interface. Ratio of reduction of mobility at negative control gate voltage is larger at BG drive than that of TG drive. It may be caused by strong roughness of BG  $SiO_2/Si$  interface caused by CMP process.

The developed in this research is different from groundplane 4T metal-oxide-semiconductor (MOS) field-effect transistors (FETs) because the TFT developed in this research enable us to control  $V_{th}$  of individual TFTs. The performance reported in this paper is superior to that previously reported in pioneering work on 4T poly-Si TFTs fabricated on glass substrates [4]. The high controllability of device parameter of individual LT poly-Si TFTs enables us to the fabrication of high-speed and low-power-dissipation CMOS circuits on a glass substrate.

# 5. Conclusion

In summary, high-performance 4T E-MeDG LT poly-Si TFTs were fabricated on a glass substrate at a low temperature of 550°C. The poly-Si channel with lateral large grains was fabricated using a CLC method. Trends of threshold voltage modulation magnitude,  $\gamma = |\Delta V_{th}/\Delta V_{CG}|$ , and s.s. were consistent with theoretical prediction, but they are not exactly same values. This is owned to following. First, though our TFTs are made up of lateral large grained poly-Si film, it is not single crystalline Si but poly-Si film. Second, TFTs developed in this research is fabricated by low temperature process, thus quality of SiO<sub>2</sub> and SiO<sub>2</sub>/Si interface is inferior to those of high temperature processes. In spite that, the high controllability of device parameter of individual LT poly-Si TFTs will enable us to the fabrication of high-speed and low power-dissipation CMOS circuits on a glass substrate.

#### Acknowledgments

This study was supported in part by the Japan Society for the Promotion of Science through Grants-in-Aid for Scientific Research (C) 22560341 and (C) 25420339. A part of this work was supported by "Nanotechnology Platform Program" of the Ministry of Education, Culture, Sports, Science and Technology (MEXT), Japan.

## References

- A. O. Adan, S. Ono, H. Shibayama, and R. Miyake, "Analysis of submicron double-gated polysilicon MOS thin film transistors," Tech. Dig. 1990 IEDM, pp.399–402, 1990.

- [2] A. O. Adan, K. Suzuki, H. Shibayama, and R. Miyake, "A half micron SRAM cell using a double-gated self-aligned polysilicon PMOS thin film transistor (TFT) load," Tech. Dig. 1990 VLSI Symp., pp.19–20, 1990.

- [3] A. Kumar, J. K. O. Sin, C. T. Nguyen, and P. K. Ko, "Kink-free polycrystalline silicon double-gate elevated-channel thin-film transistors," IEEE Trans. Electron. Dev., vol.45, no.12, pp.2514–2520, 1998.

- [4] K. Makihira, K. Nakagawa, and T. Asano, "Double-gate poly-Si thin-film transistors fabricated using self-aligned technology," Tech. Dig. 2001 AM-LCD, pp. 243–246, 2001.

- [5] S. Zhang, R. Han, J. K. O. Sin, and M. Chan, "A novel self-aligned double-gate TFT technology," IEEE Electron Device Lett., vol.22,

no.11, pp.530-532, 2001.

- [6] S. Zhang, R. Han, J. K. O. Sin, and M. Chan, "Implementation and characterization of self-aligned double-gate TFT with thin channel and thick source/drain," IEEE Trans. Electron. Dev., vol.49, no.5, pp.718–724, 2002.

- [7] A. Hara, M. Takei, K. Yoshino, F. Takeuchi, M. Chida, and N. Sasaki, "Self-aligned top and bottom metal double gate low temperature poly-Si TFT fabricated at 550°C on non-alkali glass substrate by using DPSS CW laser lateral crystallization method," Tech. Dig. 2003 IEDM, pp.8.6.1–8.6.4, 2003.

- [8] Y.-C. Wu, T.-C. Chang, C.-Y. Chang, C.-S. Chen, C.-H. Tu, P.-T. Liu, H.-W. Zan, and Y.-H. Tai, "High-performance polycrystalline silicon thin-film transistor with multiple nanowire channels and lightly doped drain structure," Appl. Phys. Lett., vol.84, no.19, pp.3822–3824, 2004.

- [9] Z. Xiong, H. Liu, C. Zhu, and J. K. O. Sin, "A new polysilicon CMOS self-aligned double-gate TFT technology," IEEE Trans. Electron. Dev., vol.52, no.12, pp.2629–2633, 2005.

- [10] M.-S. Shieh, J.-Y. Sang, C.-Y. Chen, S.-D. Wang, and T.-F. Lei, "Electrical characteristics and reliability of multi-channel polycrystalline silicon thin-film transistors," Jpn. J. Appl. Phys., vol.45, no.4B, pp.3159–3164, 2006.

- [11] C.-C. Tsai, K.-F. Wei, Y.-J. Lee, H. H. Chen, J.-L. Wang, I.-C. Lee, and H.-C. Cheng, "High-performance short-channel double-gate low-temperature polysilicon thin-film transistors using excimer laser crystallization," IEEE Electron Device Lett., vol.28, no.11, pp.1010–1013, 2007.

- [12] M. Im, J.-W. Han, H. Lee, L.-E. Yu, S. Kim, C.-H. Kim, S. C. Jeon, K. H. Kim, G. S. Lee, J. S. Oh, Y. C. Park, H. M. Lee, and Y.-K. Choi, "Multiple-gate CMOS thin-film transistor with polysilicon nanowire," IEEE Electron Device Lett., vol.29, no.1, pp.102–105, 2008.

- [13] H. Yin, W. Xianyu, A. Tikhonovsky, and Y. S. Park, "Scalable 3-D fin-like poly-Si TFT and its nonvolatile memory application," IEEE Trans. Electron. Dev., vol.55, no.2, pp.578–584, 2008.

- [14] T.-C. Liao, S.-W. Tu, M. H. Yu, W.-K. Lin, C.-C. Liu, K.-J. Chang, Y.-H. Tai, and H.-C. Cheng, "Novel gate-all-around poly-Si TFTs with multiple nanowire channels," IEEE Electron Device Lett., vol.29, no.8, pp.889–891, 2008.

- [15] H.-H. Hsu, T.-W. Liu, L. Chan, C.-D. Lin, T.-Y. Huang, and H.-C. Lin, "Fabrication and characterization of multiple-gated poly-Si nanowire thin-film transistors and impacts of multiple-gate structures on device fluctuations," IEEE Trans. Electron Dev., vol.55, no.11, pp.3063–3069, 2008.

- [16] J.-T. Sheu, P.-C. Huang, T.-S. Sheu, C.-C. Chen, and L.-A. Chen, "Characteristics of gate-all-around twin poly-Si nanowire thin-film transistors," IEEE Electron Device Lett., vol.30, no.2, pp.139–141, 2009.

- [17] H.-H. Hsu, H.-C. Lin, L. Chan, and T.-Y. Huang, "Threshold-voltage fluctuation of double-gated poly-Si nanowire field-effect transistor," IEEE Electron Device Lett., vol.30, no.3, pp.243–245, 2009.

- [18] H.-C. Lin, W.-C. Chen, C.-D. Lin, and T.-Y. Huang, "Performance enhancement in double-gated poly-Si nanowire transistors with reduced nanowire channel thickness," IEEE Electron Device Lett., vol.30, no.6, pp.644–646, 2009.

- [19] P.-C. Huang, L.-A. Chen, and J.-T. Sheu, "Electric-field enhancement of a gate-all-around nanowire thin-film transistor memory," IEEE Electron Device Lett., vol.31, no.3, pp.216–218, 2010.

- [20] J.-W. Han, S.-W. Ryu, D.-H. Kim, and Y.-K. Choi, "Polysilicon channel TFT with separated double-gate for Unified RAM (URAM)—unified function for nonvolatile SONOS flash and highspeed capacitorless 1T-DRAM," IEEE Trans. Electron. Dev., vol.57, no.3, pp.601–607, 2010.

- [21] C.-M. Lee and B.-Y. Tsui, "A high-performance 30-nm gate-allaround poly-Si nanowire thin-film transistor with NH<sub>3</sub> plasma treatment," IEEE Electron Device Lett., vol.31, no.7, pp.683–685, 2010.

- [22] H.-H. Hsu, H.-C. Lin, and T.-Y. Huang, "Origins of performance en-

hancement in independent double-gated poly-Si nanowire devices," IEEE Trans. Electron. Dev., vol.57, no.4, pp.905–912, 2010.

- [23] S.-I. Kuroki, X. Zhu, K. Kotani, and T. Ito, "Enhancement of current drivability of nanograting polycrystalline silicon thin-film transistors," Jpn. J. Appl. Phys., vol.49, no.4S, pp.04DJ11-1–04DJ11-5, 2010.

- [24] H. J. H. Chen, J.-R. Jhang, C.-J. Huang, S.-Z. Chen, and J.-C. Huang, "Poly-Si TFTs with three-dimensional finlike channels fabricated using nanoimprint technology," IEEE Electron Device Lett., vol.32, no.2, pp.155–157, 2011.

- [25] A. Hara, T. Sato, K. Kondo, K. Hirose, and K. Kitahara, "Selfaligned metal double-gate low-temperature polycrystalline silicon thin-film transistors on glass substrate using back-surface exposure," Jpn. J. Appl. Phys., vol.50, no.2R, pp.021401-1–021401-4, 2011.

- [26] Y.-H. Lu, P.-Y. Kuo, Y.-H. Wu, Y.-H. Chen, and T.-S. Chao, "Novel sub-10-nm gate-all-around Si nanowire channel poly-Si TFTs with raised source/drain," IEEE Electron Device Lett., vol.32, no.2, pp.173–175, 2011.

- [27] T.-K. Kang, T.-C. Liao, C.-M. Lin, H.-W. Liu, and H.-C. Cheng, "High-performance single-crystal-like nanowire poly-Si TFTs with spacer patterning technique," IEEE Electron Device Lett., vol.32, no.3, pp.330–332, 2011.

- [28] C.-J. Su, T.-I. Tsai, Y.-L. Liou, Z.-M. Lin, H.-C. Lin, and T.-S. Chao, "Gate-all-around junctionless transistors with heavily doped polysilicon nanowire channels," IEEE Electron Device Lett., vol.32, no.4, pp.521–523, 2011.

- [29] H.-H. Hsu, H.-C. Lin, C.-W. Luo, C.-J. Su, and T.-Y. Huang, "Impacts of multiple-gated configuration on the characteristics of poly-Si nanowire SONOS devices," IEEE Trans. Electron. Dev., vol.58, no.3, pp.641–649, 2011.

- [30] S. Fujii, S.-I. Kuroki, K. Kotani, and T. Ito, "Strain-induced back channel electron mobility enhancement in polycrystalline silicon thin-film transistors fabricated by continuous-wave laser lateral crystallization," Jpn. J. Appl. Phys., vol.50, no.4, pp.04DH10-1– 04DH10-5, 2011.

- [31] T. T. Le, H. Y. Yu, Y. Sun, N. Singh, X. Zhou, N. Shen, G. Q. Lo, and D. L. Kwong, "High-performance poly-Si vertical nanowire thin-film transistor and the inverter demonstration," IEEE Electron Device Lett., vol.32, no.6, pp.770–772, 2011.

- [32] T.-K. Kang, T.-C. Liao, C.-M. Lin, H.-W. Liu, F.-H. Wang, and H.-C. Cheng, "Gate-all-around poly-Si TFTs with single-crystallike nanowire channels," IEEE Electron Device Lett., vol.32, no.9, pp.1239–1241, 2011.

- [33] H.-B. Chen, Y.-C. Wu, C.-K. Yang, L.-C. Chen, J.-H. Chiang, and C.-Y. Chang, "Impacts of poly-Si nanowire shape on gate-all-around flash memory with hybrid trap layer," IEEE Electron Device Lett., vol.32, no.10, pp.1382–1384, 2011.

- [34] H.-H. Hu, Y.-R. Jheng, Y.-C. Wu, M.-F. Hung, and G.-W. Huang, "Low-frequency noise in poly-Si TFT SONOS memory with a trigate nanowire structure," IEEE Electron Device Lett., vol.32, no.12, pp.1698–1700, 2011.

- [35] L.-J. Chen, Y.-C. Wu, J.-H. Chiang, M.-F. Hung, C.-W. Chang, and P.-W. Su, "Comprehensive study of pi-gate nanowires poly-Si TFT nonvolatile memory with an HfO<sub>2</sub> charge trapping layer," IEEE Trans. NanoTechnol., vol.10, no.2, pp.260–265, 2011.

- [36] M.-F. Hung, Y.-C. Wu, and Z.-Y. Tang, "High-performance gateall-around polycrystalline silicon nanowire with silicon nanocrystals nonvolatile memory," Appl. Phys. Lett., vol.98, no.16, pp.162108-1– 162108-3, 2011.

- [37] H.-W. Liu, S.-M. Chiou, H.-C. Huang, J. Gong, and F.-H. Wang, "Superior reliability of gate-all-around polycrystalline silicon thinfilm transistors with vacuum cavities next to gate oxide edges," Jpn. J. Appl. Phys., vol.50, no.1, pp.014202-1–014202-6, 2011.

- [38] P.-C. Huang, L.-A. Chen, C.-C. Chen, and J.-T. Sheu, "Minimizing variation in the electrical characteristics of gate-all-around thin film transistors through the use of multiple-channel nanowire and NH<sub>3</sub> plasma treatment," Microelectron. Eng., vol.91, pp.54–58, Mar.

2012.

- [39] Y. Liu, T. Kamei, T. Matsukawa, K. Endo, S. O'uchi, J. Tsukada, H. Yamauchi, Y. Ishikawa, T. Hayashida, K. Sakamoto, A. Ogura, and M. Masahara, "Variability analysis of scaled crystal channel and poly-Si channel fin FETs," IEEE Trans. Electron. Dev., vol.59, no.3, pp.573–581, 2012.

- [40] T.-C. Liao, T.-K. Kang, C.-M. Lin, C.-Y. Wu, and H.-C. Cheng, "Gate-all-around polycrystalline-silicon thin-film transistors with self-aligned grain-growth nanowire channels," Appl. Phys. Lett., vol.100, no.9, 093501-1–093501-3, 2012.

- [41] H.-B. Chen, Y.-C. Wu, L.-C. Chen, J.-H. Chiang, C.-K. Yang, and C.-Y. Chang, "High-reliability trigate poly-Si channel flash memory cell with Si-nanocrystal embedded charge-trapping layer," IEEE Electron Device Lett., vol.33, no.4, pp.537–539, 2012.

- [42] C.-H. Kuo, H.-C. Lin, I.-C. Lee, H.-C. Cheng, and T.-Y. Huang, "A novel scheme for fabricating CMOS inverters with poly-Si nanowire channels," IEEE Electron Device Lett., vol.33, no.6, pp.833–835, 2012.

- [43] C.-Y. Wu, T.-C. Liao, Y.-T. Liu, M. H. Yu, and H.-C. Cheng, "A novel polysilicon field-enhanced nanowire thin-film transistor with the TiN-hafnia-nitride-vacuum-silicon (THNVAS) structure for nonvolatile memory applications," J. Nanosci. Nanotechnol., vol.12, no.7, pp.5276–5282, 2012.

- [44] T.-K. Kang, T.-C. Liao, and C.-K. Wang, "Gate bias stresses of gateall-around poly-Si TFTs with multiple nanowire channels," IEEE Trans. Electron. Dev., vol.59, no.8, pp.2173–2179, 2012.

- [45] H.-H. Hu, Y.-R. Jheng, Y.-C. Wu, M.-F. Hung, and G.-W. Huang, "Low-frequency noise in SONOS-TFT with a trigate nanowire structure under program/erase operation," IEEE Electron Device Lett., vol.33, no.9, pp.1276–1278, 2012.

- [46] T.-K. Kang, T.-C. Liao, and Y.-Y. Yang, "Self-heating and kink effects in SLS single-crystal-like nanowire," Transistors IEEE Trans. on Electron Devices, vol.59, no.10, pp.2787–2794, 2012.

- [47] T.-Y. Liu, S.-C. Lo, and J.-T. Sheu, "Gate-all-around single-crystallike poly-Si nanowire TFTs with a steep-subthreshold slope," IEEE Electron Device Lett., vol.34, no.4, pp.523–525, 2013.

- [48] Y. Liu, T. Kamei, T. Matsukawa, K. Endo, S. O'uchi, J. Tsukada, H. Yamauchi, Y. Ishikawa, T. Hayashida, K. Sakamoto, A. Ogura, and M. Masahara, "Gate structure dependence of variability in polycrystalline silicon fin-channel flash memories," Jpn. J. Appl. Phys., vol.52, no.6, pp.06GE01-1–06GE01-5, 2013.

- [49] T. K. Kang, "High-performance SLS nanowire TFTs with dual-gate structure," IEEE Trans. Eletron Dev., vol.60, no.7, pp.2276–2281, 2013.

- [50] H. Ogata, K. Ichijo, K. Kondo, and A. Hara, "Self-aligned planar metal double-gate polycrystalline-silicon thin-film transistors fabricated at low temperature on glass substrate," IEICE Trans. Electron., vol.E96-C, no.2, pp.285–288, 2013.

- [51] S. Sasaki, H. Ogata, and A. Hara, "Self-aligned planar metal doublegate low-temperature polycrystalline-silicon thin-film transistors on glass substrate," Proc. 2013 AM-FPD, pp.251–254, 2013.

- [52] A. Hara, F. Takeuchi, M. Takei, K. Suga, K. Yoshino, M. Chida, Y. Sano, and N. Sasaki, "High-performance polycrystalline silicon thin film transistors on non-alkali glass produced using continuous wave laser lateral crystallization," Jpn. J. Appl. Phys., vol.41, no.3B, pp.L311–L313, 2002.

- [53] A. Hara, M. Takei, F. Takeuchi, K. Suga, K. Yoshino, M. Chida, T. Kakehi, Y. Ebiko, Y. Sano, and N. Sasaki, "High performance low temperature polycrystalline silicon thin film transistors on nonalkaline glass produced using diode pumped solid state continuous wave laser lateral crystallization," Jpn. J. Appl. Phys., vol.43, no.4A, pp.1269–1276, 2004.

- [54] Y. Shika, T. Bessho, Y. Okabe, H. Ogata, S. Kamo, K. Kitahara, and A. Hara, "Impact of the hydrogenation process on the performance of self-aligned metal double-gate low-temperature polycrystallinesilicon thin-film transistors," Jpn. J. Appl. Phys., vol.52, no.3, pp.03BB01-1–03BB01-5, 2013.

- [55] M. Masahara, Y. Liu, K. Sakamoto, K. Endo, T. Matsukawa, K. Ishii, T. Sekigawa, H. Yamauchi, H. Tanoue, S. Kanemaru, H. Koike, and E. Suzuki, "Demonstration, analysis, and device design considerations for independent DG MOSFETs," IEEE Trans. Electron. Dev., vol.52, no.9, pp.2046–2053, 2005.

- [56] M. Masahara, S. O'uchi, Y. Liu, K. Sakamoto, K. Endo, T. Matsukawa, T. Sekigawa, H. Koike, and E. Suzuki, "Optimum gate workfunction for V<sub>th</sub>-controllable four-terminal-driven double-gate MOSFETs (4T-XMOSFETs)—Band-edge workfunction versus midgap workfunction," IEEE Trans. NanoTechnol., vol.5, no.6, pp.716–722, 2006.

- [57] Y. Taur and T. H. Ning, Fundamentals of Modern VLSI Devices, 2nd edition, p.529, Cambridge University Press, 2009.

- [58] A. Kamgar, S. J. Hillenius, H.-I. L. Cong, R. L. Field, W. S. Lindenberger, G. K. Celler, L. E. Trimble, and T. T. Sheng, "Ultra-fast (0.5-μm) CMOS circuits in fully depleted SOI films," IEEE Trans. Electron. Dev., vol.39, no.3, pp.640–647, 1992.

Akito Hara received the B.S. degree in applied physics from Science University of Tokyo in 1983. He received M.S. and Ph.D. degrees in physics from Tohoku University in 1985 and 1996, respectively. During 1985–2006, he worked at Fujitsu Laboratories Limited. In 2006, he was associate professor of electronic engineering of Tohoku Gakuin University. He has been professor since 2008. One of his current interests is TFT technologies and another is lattice defects, impurities, and nano-structure in Semiconductors.

Shinya Kamo received the B.S. degree in electronic engineering of Tohoku Gakuin University at 2012. He is currently working toward M.S. degree. His research interest is TFT technologies.

Tadashi Satoreceived the B.S. and M.S. degrees in Engineering from Tohoku-Gakuin University in 2008 and 2010, respectively. He is now enrolled in Hiroshima University Research Institute for Nanodevice and Bio Systems (RNBS) as a researcher of nanotechnology platform.